#### ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE

## FACULTE DES SCIENCES ET TECHNIQUES DE L'INGENIEUR SECTION D'ELECTRICITE

# CIRCUITS ET SYSTEMES ELECTRONIQUES

**ELECTRICITE**

A. Ionescu M. Kayal

Lausanne, septembre 2021 Nouvelle édition

# CIRCUITS ET SYSTEMES ELECTRONIQUES

#### LES AMPLIFICATEURS A UN TRANSISTOR

L'AMPLIFICATEUR DIFFERENTIEL

LES ALIMENTATIONS STABILISEES

LINEAIRES SERIE

LES AMPLIFICATEURS DE PUISSANCE

CONVERTISSEURS

ANALOGIQUES / NUMERIQUES

ET

NUMERIQUES / ANALOGIQUES

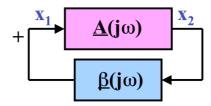

LA REACTION NEGATIVE

LA STABILITE DES MONTAGES

A REACTION NEGATIVE

BOUCLES A VERROUILLAGE DE PHASE (PLL)

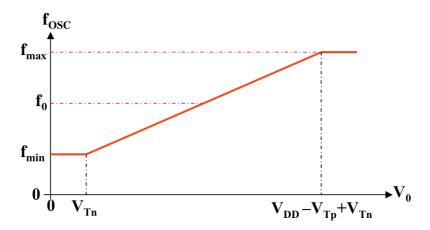

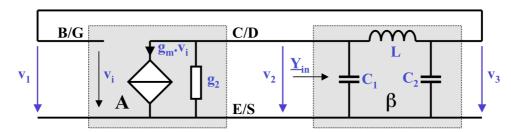

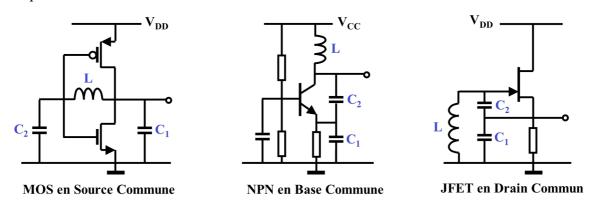

OSCILLATEURS COMMANDES EN TENSION (VCO)

SYNTHETISEURS DE FREQUENCE A PLL

## LES AMPLIFICATEURS A UN TRANSISTOR

### 1. LES AMPLIFICATEURS A UN TRANSISTOR

|       |                                                                      | page |

|-------|----------------------------------------------------------------------|------|

| 1.1.  | MODELES NON LINEAIRES DES TRANSISTORS                                | 3    |

| 1.1.1 | Modèle non-linéaire du transistor bipolaire en mode normal direct    | 3    |

| 1.1.2 | Modèle non-linéaire du transistor MOS en saturation                  | 4    |

| 1.2.  | MODELE LINEAIRE DES TRANSISTORS                                      | 5    |

| 1.3.  | COMPARAISON BIPOLAIRE – MOS                                          | 5    |

| 1.4.  | MONTAGES DE BASE A UN TRANSISTOR                                     | 6    |

| 1.4.1 | Définition des paramètres du quadripôle équivalent                   | 6    |

| 1.4.2 | Montage Emetteur Commun                                              | 7    |

| 1.4.3 | Montage Base Commune                                                 | 8    |

| 1.4.4 | Montage Collecteur Commun                                            | 10   |

| 1.4.5 | Montage Emetteur Commun Dégénéré                                     | 12   |

| 1.4.6 | Montage Source Commune                                               | 14   |

| 1.4.7 | Montage Grille Commune                                               | 15   |

| 1.4.8 | Montage Drain Commun                                                 | 16   |

| 1.4.9 | Montage Source Commune Dégénérée                                     | 17   |

| 1.5.  | RESISTANCES AUX ACCES DES TRANSISTORS                                | 19   |

| 1.5.1 | Résumé synthétique des résistances aux accès du transistor bipolaire | 19   |

| 1.5.2 | Résumé synthétique des résistances aux accès du transistor           |      |

|       | MOS                                                                  | 20   |

#### 1.1. MODELES NON LINEAIRES DES TRANSISTORS

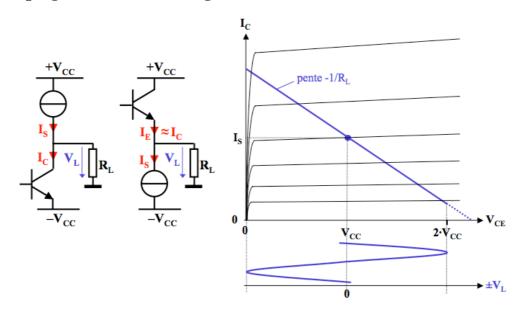

Pour faire des fonctions analogiques, en particulier des amplificateurs, on utilise des transistors en source de courant commandée, c'est-à-dire en mode normal pour les transistors bipolaires, et en mode saturé pour les transistors à effet de champ JFET et MOS.

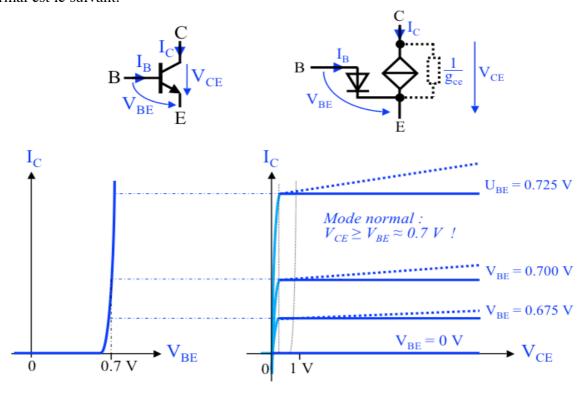

#### 1.1.1 Modèle non-linéaire du transistor bipolaire en mode normal direct

Le modèle non-linéaire, appelé aussi modèle "grands signaux", du transistor NPN en mode normal est le suivant:

Les équations caractéristiques du modèle idéal (traits pleins) sont:

$$I_C = I_s \cdot e^{\frac{V_{BE}}{U_T}}$$

et  $I_C = \beta \cdot I_B$  tant que  $V_{CE} \ge V_{BE}$  avec:  $U_T = \frac{k \cdot T}{q} \cong 26 \text{mV}$  à 300°K

Où  $I_s$  et le gain en courant  $\beta$  sont des paramètres propres à chaque composant.

Pour modéliser le fait que les caractéristiques  $I_C = f(V_{CE})$  réelles (pointillés) ne sont pas parfaitement horizontales, appelé effet Early, une conductance  $g_{ce}$  (en pointillé) est ajoutée en parallèle avec la source commandée, ce qui donne:

$$I_C = I_s \cdot e^{\frac{V_{BE}}{U_T}} + g_{ce} \cdot V_{CE}$$

Pour le transistor bipolaire PNP, la diode base-émetteur ainsi que tous les courants et tensions sont inversés par rapport au NPN. Ce qui donne pour le modèle idéal:

$$I_C = I_s \cdot e^{\frac{V_{EB}}{U_T}} \quad \text{et} \quad I_C = \beta \cdot I_B \quad \ \ \text{tant que } \ V_{\text{EC}} {\geq} V_{\text{EB}}$$

Et en tenant compte de la conductance g<sub>ce</sub> modélisant l'effet Early:

$$I_C = I_s \cdot e^{\frac{V_{EB}}{U_T}} + g_{ce} \cdot V_{EC}$$

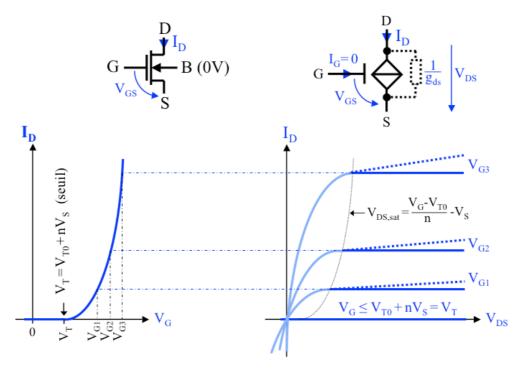

#### 1.1.2 Modèle non-linéaire du transistor MOS en saturation

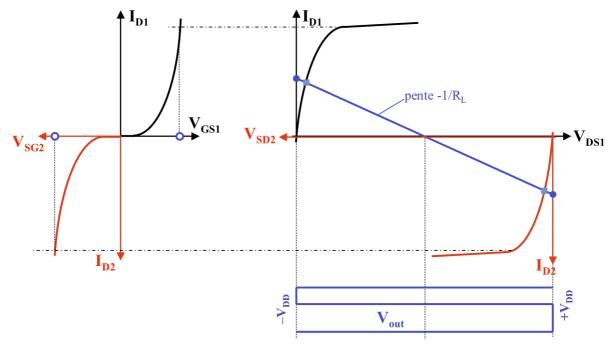

Le modèle non-linéaire, appelé aussi modèle "grands signaux", du transistor MOS en saturation est le suivant:

Pour un transistor NMOS idéal (traits pleins) en forte inversion et saturation, c-à-d avec:

$$\begin{split} &V_G \! \geq \! V_{T0} \! + \! n V_S \quad \text{ et } \quad V_D \! \geq \! \frac{V_G - V_{T0}}{n} \\ &I_D \! = \! \frac{\beta}{2n} \! \cdot \! \left( V_G - \! V_{T0} \! - \! n V_S \right)^2 \quad \text{ avec } \quad \beta \! = \! \mu_n \! \cdot \! C_{ox} \! \cdot \! \frac{W}{L} \end{split}$$

$V_{T0}$ , n,  $\mu_n$  et  $C_{ox}$  sont des paramètres technologiques, W/L est le rapport largeur/longueur du canal.

Pour un MOS discret, avec la source généralement reliée au substrat, et donc  $V_s = 0$ , ainsi que pour un MOS intégré dans une technologie moderne avec  $n \approx 1$ , les équations deviennent:

$$I_{D} = \frac{\beta}{2} \cdot (V_{GS} - V_{T0})^{2}$$

si  $V_{DS} \ge V_{GS} - V_{T0}$

Pour modéliser le fait que les caractéristiques  $I_D = f(V_{DS})$  réelles (pointillés) ne sont pas parfaitement horizontales, à cause de la modulation de la longueur du canal, une conductance  $g_{ds}$  (en pointillé) est ajoutée en parallèle avec la source commandée, ce qui donne:

$$I_{D} = \frac{\beta}{2} \cdot (V_{GS} - V_{T0})^{2} + g_{ds} \cdot V_{DS}$$

Pour le transistor PMOS, tous les courants et tensions sont inversés par rapport au NMOS, et les paramètres technologiques ont des valeurs différentes. Ce qui donne:

$$\begin{split} I_D &= \frac{\beta}{2} \cdot (V_{SG} - V_{T0})^2 \quad \text{si} \quad V_{SD} \ge V_{SG} - V_{T0} \quad \text{modèle idéal} \\ I_D &= \frac{\beta}{2} \cdot (V_{SG} - V_{T0})^2 + g_{ds} \cdot V_{SD} \quad \text{avec modulation de longueur du canal} \end{split}$$

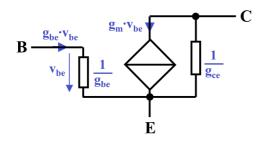

#### 1.2. MODELE LINEAIRE DES TRANSISTORS

Le modèle linéaire, appelé aussi "petits signaux", d'un transistor est obtenu en linéarisant (dérivant) les lois "grands signaux" autour d'un point de repos. On obtient ainsi:

## Modèle "petits signaux" du transistor bipolaire

$$g_{m} = \frac{I_{C0}}{U_{T}}$$

$g_{be} = \frac{I_{C0}}{\beta \cdot U_{T}}$   $g_{ce} \approx \frac{I_{C0}}{V_{A}}$

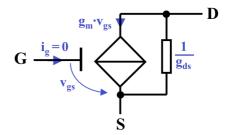

## Modèle "petits signaux" du transistor MOS

$$g_{\rm m} = \sqrt{2 \cdot \beta \cdot I_{\rm D0}} = \beta \cdot (V_{\rm GS0} - V_{\rm T0})$$

$g_{\rm ds} \approx \frac{I_{\rm D0}}{V_{\rm A}}$

Les paramètres "petits signaux" sont fonction du courant de repos et des paramètres technologiques et géométriques du transistor, dont la tension "Early"  $V_A$ .

Pour tout transistor bipolaire:  $g_m >> g_{be} >> g_{ce}$

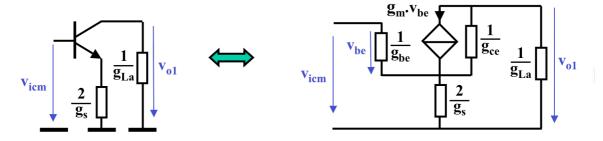

Le schéma "petit signaux" d'un PNP est identique à celui d'un NPN.

Un MOS peut avoir g<sub>m</sub> comparable à g<sub>ds</sub>

Le schéma "petit signaux" d'un PMOS est identique à celui d'un NMOS.

#### 1.3. COMPARAISON BIPOLAIRE - MOS

#### **Avantage bipolaire:**

- Loi exponentielle (et donc son inverse log) permettant la multiplication analogique.

- g<sub>m</sub> plus élevé à courant donné.

- $V_{BE}$  quasi constant  $\approx 0.7 \text{ V}$ .

- Densité de courant plus élevée par unité de surface.

- Moindre sensibilité aux variations du processus de fabrication.

- Zone utile  $I_C = f(V_{CE})$  en source de courant plus étendue, en pratique dès que  $V_{CE} \ge 0.2 \, V$ .

#### **Avantage MOS:**

- Surface minimale des dispositifs intégrés, très haute densité.

- Circuits à très faible puissance.

- Processus de fabrication à haut rendement.

- Courant de grille nul en DC et capacité de grille formant une mémoire intrinsèque.

- En circuit intégré, plusieurs modes de fonctionnement possibles: faible, moyenne ou forte inversion, suivant que  $V_G$  et inférieur, à peu près égal ou supérieur à  $V_{T0}$ , aboutissant à des comportements très différents (voir cours "Structures analogiques" du Prof. Kayal).

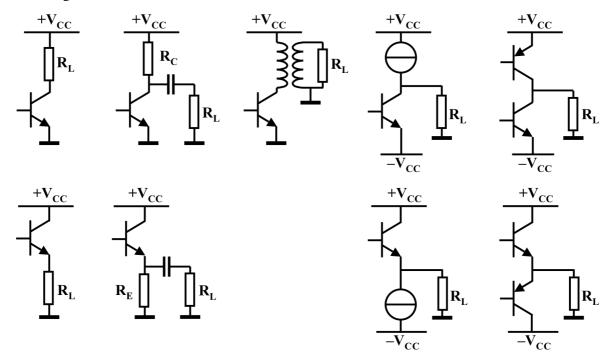

#### 1.4. MONTAGES DE BASE A UN TRANSISTOR

#### 1.4.1 Définition des paramètres du quadripôle équivalent

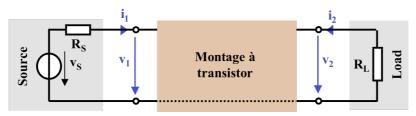

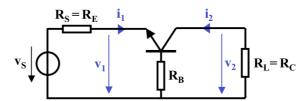

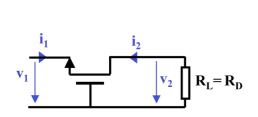

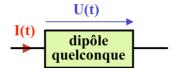

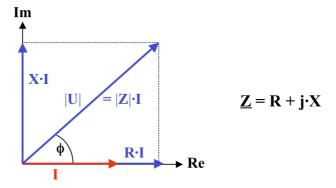

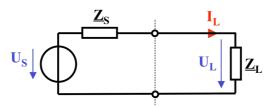

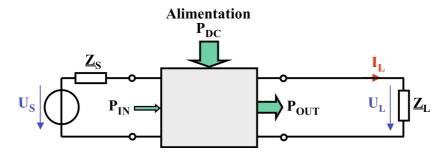

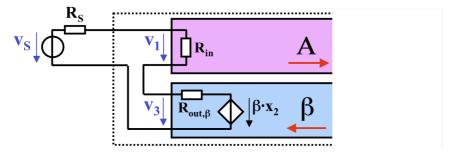

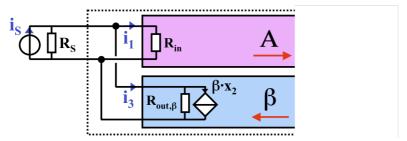

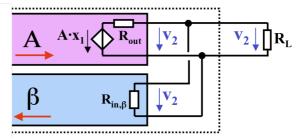

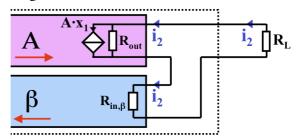

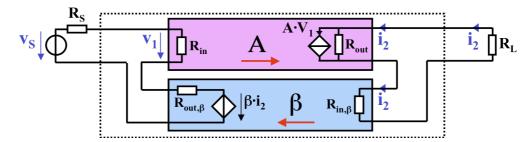

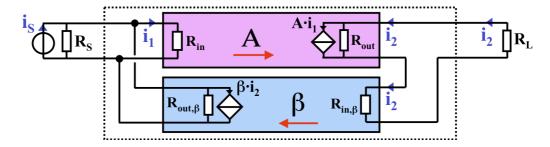

Un amplificateur à un transistor peut être représenté par un quadripôle, dont l'entrée est connectée à une source réelle (avec sa résistance interne), et la sortie à une charge. La source réelle peut aussi bien être représentée par son équivalent Thévenin, comme ci-dessous, que par son équivalent Norton.

On cherche à établir les relations liant les grandeurs pratiquement accessibles que sont  $v_1$ ,  $i_1$ ,  $v_2$  et  $i_2$ . On s'intéresse plus particulièrement aux paramètres suivants:

- le gain en tension:  $A_v = \frac{v_2}{v_1}$  avec une charge  $R_L$  donnée

- la résistance d'entrée:  $R_{in} = \frac{v_1}{i_1}$  avec une charge  $R_L$  donnée

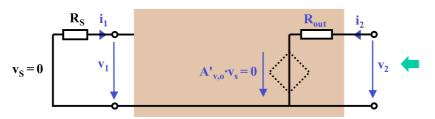

- la résistance de sortie:  $R_{out} = \frac{v_2}{i_2}$  avec  $v_s = 0$  et une résistance de source  $R_s$  donnée

Pour déterminer R<sub>out</sub>, il faut annuler la source indépendante à l'entrée, déconnecter la charge, et calculer ou mesurer la résistance vue des bornes de sortie.

On peut aussi définir:

- le gain en courant:  $A_i = \frac{i_2}{i_1}$  avec une charge  $R_L$  donnée

- la transrésistance:  $R_m = \frac{V_2}{i_1}$  avec une charge  $R_L$  donnée

- la transconductance:  $G_m = \frac{i_2}{v_1}$  avec une charge  $R_L$  donnée

En outre, tout quadripôle satisfait les relations générales:

$$A_{v} = -\frac{A_{i} \cdot R_{L}}{R_{in}} \qquad A_{v} = \frac{R_{m}}{R_{in}} \qquad A_{v} = -G_{m} \cdot R_{L}$$

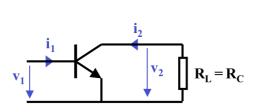

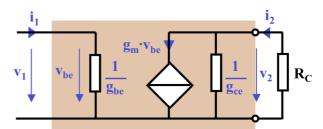

#### 1.4.2 Montage Emetteur Commun

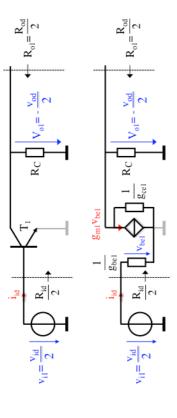

Dans le schéma "petits signaux", l'émetteur est à la masse, borne commune à l'entrée et à la sortie:

$$v_1 = v_{be}$$

$$i_1 = g_{be}v_{be}$$

$$i_2 = g_mv_{be} + g_{ce}v_2$$

$$v_2 = -R_Ci_2$$

D'où:

$$A_{v} = \frac{v_{2}}{v_{1}} = \frac{-g_{m}R_{C}}{1 + g_{ce}R_{C}} = -g_{m}\left(R_{C} / / \frac{1}{g_{ce}}\right) \qquad \text{et} \qquad A_{i} = \frac{i_{2}}{i_{1}} = \frac{\beta}{1 + g_{ce}R_{C}}$$

Suivant la valeur de la charge extérieure R<sub>C</sub>, on peut simplifier ces expressions ainsi :

$$\begin{aligned} \text{si: } & R_{\text{C}} << \frac{1}{g_{\text{ce}}} & A_{\text{v}} = -g_{\text{m}}R_{\text{C}} & A_{\text{i}} = \beta \\ \\ \text{si: } & \frac{1}{g_{\text{ce}}} << R_{\text{C}} & A_{\text{v}} = -\frac{g_{\text{m}}}{g_{\text{ce}}} & A_{\text{i}} = \frac{\beta}{g_{\text{ce}}R_{\text{C}}} \end{aligned}$$

La résistance d'entrée est simplement :

$$R_{in} = \frac{v_1}{i_1} = \frac{1}{g_{he}}$$

ne dépend pas de la charge extérieure  $R_C$ .

Pour le calcul de la résistance de sortie, le schéma "petits signaux" est le suivant:

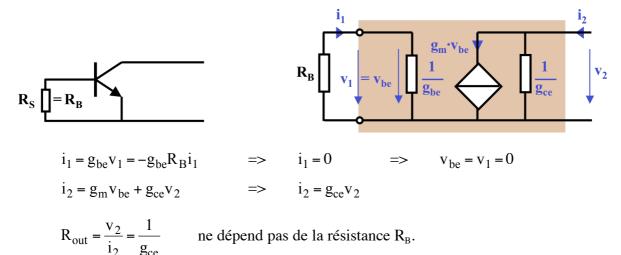

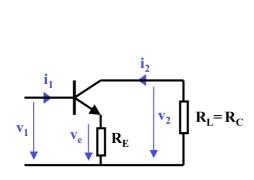

#### 1.4.3 Montage Base Commune

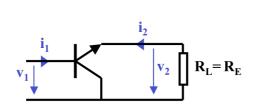

Dans le schéma "petits signaux", la base est à la masse, borne commune à l'entrée et à la sortie:

$$\begin{aligned} v_1 &= -v_{be} \\ i_1 &= g_{be}v_1 - g_mv_{be} - g_{ce}(v_2 - v_1) = g_{be}v_1 + g_mv_1 + g_{ce}(v_1 - v_2) \\ i_2 &= g_mv_{be} + g_{ce}(v_2 - v_1) = -g_mv_1 - g_{ce}(v_1 - v_2) \\ v_2 &= -R_Ci_2 \end{aligned}$$

De ces équations, en tenant compte que  $g_{ce} \ll g_{be} \ll g_m$ , on tire:

$$A_v = \frac{v_2}{v_1} = \frac{g_m R_C}{1 + g_{ce} R_C} = g_m \left( R_C // \frac{1}{g_{ce}} \right)$$

$$A_i = \frac{i_2}{i_1} = \frac{-1}{1 + \frac{g_{ce}R_C}{\beta}}$$

$$R_{in} = \frac{v_1}{i_1} = \frac{1 + g_{ce}R_C}{g_m(1 + \frac{g_{ce}R_C}{\beta})}$$

Suivant la valeur de la charge extérieure  $R_{\scriptscriptstyle C}$ , on peut simplifier ces expressions ainsi :

$$\begin{aligned} \text{si: } R_{C} << \frac{1}{g_{ce}} & A_{v} = g_{m} R_{C} & A_{i} = -1 & R_{in} = \frac{1}{g_{m}} \\ \\ \text{si: } & \frac{1}{g_{ce}} << R_{C} << \frac{\beta}{g_{ce}} & A_{v} = \frac{g_{m}}{g_{ce}} & A_{i} = -1 & R_{in} = \frac{g_{ce} R_{C}}{g_{m}} \\ \\ \text{si: } & \frac{\beta}{g_{ce}} << R_{C} & A_{v} = \frac{g_{m}}{g_{ce}} & A_{i} = \frac{-\beta}{g_{ce} R_{C}} & R_{in} = \frac{1}{g_{be}} \end{aligned}$$

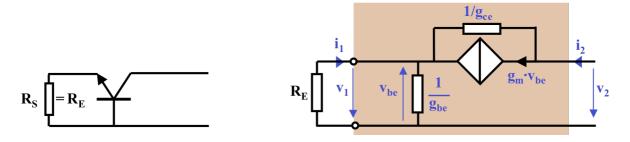

Pour le calcul de la résistance de sortie, le schéma "petits signaux" est le suivant:

$$v_1 = -v_{be} = i_2(R_E // \frac{1}{g_{be}}) = i_2 \frac{R_E}{1 + g_{be}R_E}$$

$$i_2 = g_m v_{be} + g_{ce}(v_2 - v_1) = -g_m v_1 - g_{ce}(v_1 - v_2)$$

De ces équations, en tenant compte que  $g_{ce} \ll g_{be} \ll g_m$ , on tire:

$$R_{out} = \frac{v_2}{i_2} = \frac{1}{g_{ce}} \cdot \frac{1 + g_m R_E}{1 + g_{be} R_E}$$

Suivant la valeur de la résistance globale d'émetteur R<sub>E</sub>, R<sub>out</sub> peut être simplifiée ainsi :

$$si: R_E \ll \frac{1}{g_m}$$

$$R_{out} = \frac{1}{g_{ce}}$$

$$si: \frac{1}{g_m} \ll R_E \ll \frac{1}{g_{be}}$$

$$R_{out} = \frac{1}{g_{ce}} g_m R_E$$

$$si: \frac{1}{g_{be}} \ll R_E$$

$$R_{out} = \frac{\beta}{g_{ce}}$$

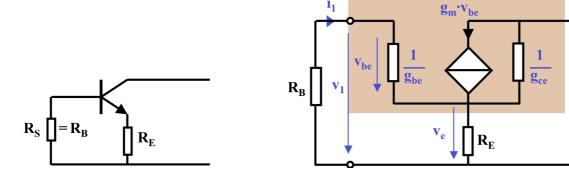

#### Remarque:

Dans la pratique, il arrive qu'il y aie une résistance  $R_B$  en série entre la base et la masse commune à l'entrée et à la sortie:

Tant que cette résistance  $R_B$  est bien inférieure à  $1/g_{be}$ , les résultats établis dans ce paragraphe restent valables.

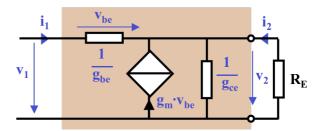

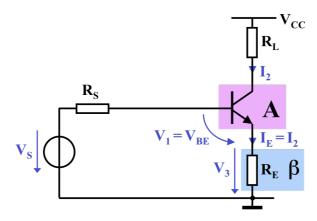

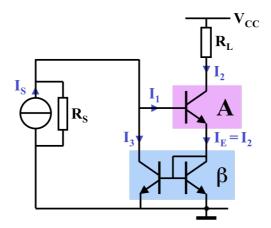

#### 1.4.4 Montage Collecteur Commun

Dans le schéma "petits signaux", le collecteur est à la masse, borne commune à l'entrée et à la sortie:

$$i_1 = g_{be}v_{be}$$

$v_1 = v_{be} + v_2$

$i_2 = -g_mv_{be} - g_{be}v_{be} + g_{ce}v_2$

$v_2 = -R_Ei_2$

De ces équations, en tenant compte que  $g_{ce}\!<\!< g_{be}\!<\!< g_m,$  on tire:

$$A_{v} = \frac{v_{2}}{v_{1}} = \frac{g_{m}R_{E}}{1 + g_{m}R_{E}}$$

$$A_{i} = \frac{i_{2}}{i_{1}} = \frac{-\beta}{1 + g_{ce}R_{E}}$$

$$R_{in} = \frac{v_{1}}{i_{1}} = \frac{1}{g_{be}} + \frac{\beta R_{E}}{1 + g_{ce}R_{E}}$$

Suivant la valeur de la charge extérieure  $R_{\scriptscriptstyle E}$ , on peut simplifier ces expressions ainsi :

$$\begin{aligned} \text{si: } & R_E << \frac{1}{g_m} \\ \text{si: } & A_v = g_m R_E <1 \qquad A_i = -\beta \qquad & R_{in} = \frac{1}{g_{be}} \\ \text{si: } & \frac{1}{g_m} << R_E << \frac{1}{g_{ce}} \\ \text{si: } & \frac{1}{g_{ce}} << R_E \qquad & A_v = 1 \qquad & A_i = -\beta \qquad & R_{in} = \beta R_E \\ \text{si: } & \frac{1}{g_{ce}} << R_E \qquad & A_v = 1 \qquad & A_i = \frac{-\beta}{g_{ce} R_E} \qquad & R_{in} = \frac{\beta}{g_{ce}} \end{aligned}$$

Pour le calcul de la résistance de sortie, le schéma "petits signaux" est le suivant:

$$i_2 = -g_m v_{be} - g_{be} v_{be} + g_{ce} v_2 = -(\beta + 1)i_1 + g_{ce} v_2$$

$v_2 = -i_1 (R_B + \frac{1}{g_{be}})$

De ces équations, en tenant compte que  $g_{ce} \ll g_{be} \ll g_m$ , on tire:

$$R_{out} = \frac{v_2}{i_2} = (\frac{1}{g_m} + \frac{R_B}{\beta}) \frac{1}{1 + g_{ce}R_B/\beta} \cong (\frac{1}{g_m} + \frac{R_B}{\beta}) / \frac{1}{g_{ce}}$$

Suivant la valeur de la résistance globale de source R<sub>B</sub>, R<sub>out</sub> peut être simplifiée ainsi :

$$si: R_{B} << \frac{1}{g_{be}}$$

$$si: \frac{1}{g_{be}} << R_{B} << \frac{\beta}{g_{ce}}$$

$$rac{1}{g_{m}}$$

$$R_{out} = \frac{R_{B}}{\beta}$$

$$rac{\beta}{g_{ce}} << R_{B}$$

$$rac{\beta}{g_{ce}} << R_{B}$$

$$rac{\beta}{g_{ce}} << R_{B}$$

$$rac{\beta}{g_{ce}} << R_{B}$$

#### Remarque:

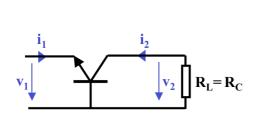

Dans la pratique, il arrive qu'il y aie une résistance  $R_C$  en série entre le collecteur et la masse commune à l'entrée et à la sortie:

Tant que cette résistance  $R_C$  est bien inférieure à  $1/g_{ce}$ , les résultats établis dans ce paragraphe restent valables.

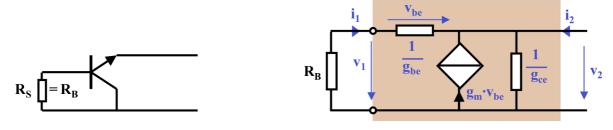

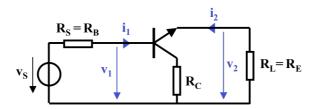

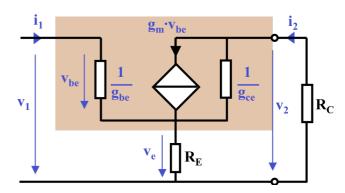

#### 1.4.5 Montage Emetteur Commun Dégénéré

Comme pour l'émetteur commun, l'entrée est sur la base et la sortie au collecteur. Mais dans le schéma "petits signaux", une résistance entre l'émetteur et la masse diminue (dégénère) le gain A<sub>v</sub>.

$$i_{1} = g_{be}v_{be}$$

$$v_{1} = v_{be} + v_{e}$$

$$v_{e} = (g_{m}v_{be} + g_{be}v_{be} + g_{ce}(v_{2} - v_{e}))R_{E}$$

$$i_{2} = g_{m}v_{be} + g_{ce}(v_{2} - v_{e})$$

$$v_{2} = -R_{C}i_{2}$$

De ces équations, sachant que  $g_{ce} \ll g_{be} \ll g_{m}$ , on tire:

$$A_{v} = \frac{v_{2}}{v_{1}} = \frac{-g_{m}R_{C}(1 - g_{ce}R_{E}/\beta)}{1 + g_{m}R_{E} + g_{ce}R_{C}(1 + g_{be}R_{E})}$$

$$A_i = \frac{i_2}{i_1} = \frac{\beta (1 - g_{ce} R_E / \beta)}{1 + g_{ce} (R_E + R_C)}$$

$$R_{in} = \frac{v_1}{i_1} = \frac{1 + g_m R_E + g_{ce} R_C (1 + g_{be} R_E)}{g_{be} (1 + g_{ce} (R_E + R_C))}$$

Dans la pratique,  $R_E$  est presque toujours bien inférieure à  $\beta/g_{ce}$ . Le terme  $g_{ce}R_E/\beta$  est alors négligeable p.r. à 1, et l'on peut établir les expressions simplifiées suivantes :

$$A_{v} = \frac{-g_{m}R_{C}}{1 + g_{m}R_{E} + g_{ce}R_{C}(1 + g_{be}R_{E})} = \frac{-g_{m}\left[R_{C} / \left(\frac{1}{g_{ce}} \cdot \frac{1 + g_{m}R_{E}}{1 + g_{be}R_{E}}\right)\right]}{1 + g_{m}R_{E}}$$

$$A_{i} = \frac{\beta}{1 + g_{ce}(R_{E} + R_{C})}$$

$$R_{in} = \frac{1 + g_{m}R_{E} + g_{ce}R_{C}(1 + g_{be}R_{E})}{g_{be}(1 + g_{ce}(R_{E} + R_{C}))}$$

Pour des valeurs de la charge extérieure R<sub>C</sub> pas trop élevées, ces expressions deviennent:

$$R_{C} << \frac{1}{g_{ce}} \cdot \frac{1 + g_{m}R_{E}}{1 + g_{be}R_{E}} \qquad \Rightarrow \qquad A_{v} = \frac{-g_{m}R_{C}}{1 + g_{m}R_{E}} \quad \text{tendant vers} : A_{v} = -\frac{R_{C}}{R_{E}} \quad \text{si} \quad \frac{1}{g_{m}} << R_{E}$$

$$R_{in} = \frac{1/g_{be} + \beta R_{E}}{1 + g_{ce}(R_{E} + R_{C})}$$

Si la somme  $(R_E+R_C)$  reste plus petite que  $1/g_{ce}$ ,  $R_{in}$  et  $A_i$  deviennent indépendants de la charge:

$$(R_E + R_C) \ll \frac{1}{g_{ce}}$$

=>  $R_{in} = \frac{1}{g_{be}} + \beta R_E$  et  $A_i = \beta$

Si, par contre, la valeur de la charge extérieure R<sub>C</sub> est très élevée:

$$R_{C} >> \frac{1}{g_{ce}} \cdot \frac{1 + g_{m}R_{E}}{1 + g_{be}R_{E}} \qquad \Rightarrow \qquad A_{v} = \frac{-g_{m}}{g_{ce}(1 + g_{be}R_{E})} \qquad \qquad A_{i} = \frac{\beta}{g_{ce}R_{C}}$$

$$R_{in} = \frac{1}{g_{be}} + R_{E}$$

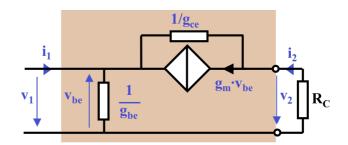

Pour le calcul de la résistance de sortie, le schéma "petits signaux" est le suivant :

$$\begin{aligned} v_e &= i_2 (R_E / / (R_B + \frac{1}{g_{be}}) = i_2 \frac{R_E (1 + g_{be} R_B)}{1 + g_{be} (R_B + R_E)} \\ v_{be} &= \frac{1/g_{be}}{R_B + 1/g_{be}} v_e = \frac{1}{1 + g_{be} R_B} v_e \\ v_2 &= v_e + \frac{1}{g_{ce}} (i_2 - g_m v_{be}) \end{aligned}$$

De ces équations, en tenant compte que  $g_{ce} \ll g_{be} \ll g_{m}$ , on tire:

$$R_{out} = \frac{v_2}{i_2} = \frac{1}{g_{ce}} \cdot \frac{1 + g_m R_E + g_{be} R_B (1 + g_{ce} R_E)}{1 + g_{be} (R_B + R_E)} = > \frac{1}{g_{ce}} \le R_{out} \le \frac{\beta}{g_{ce}}$$

Tant que  $R_E$  est inférieure à  $1/g_{ce}$ , cette expression se simplifie ainsi:

$$R_E \ll \frac{1}{g_{ce}}$$

=>  $R_{out} = \frac{1}{g_{ce}} \cdot \frac{1 + g_m R_E + g_{be} R_B}{1 + g_{be} (R_B + R_E)}$

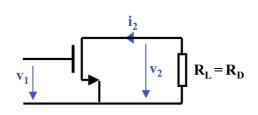

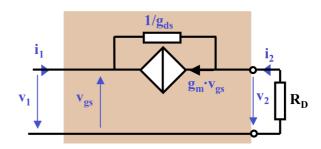

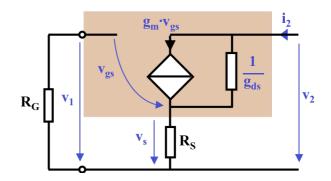

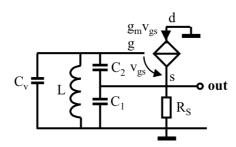

#### 1.4.6 Montage Source Commune

Dans le schéma "petits signaux", la source est à la masse, borne commune à l'entrée et à la sortie:

$$v_2 = -g_m v_{gs} (\frac{1}{g_{ds}} // R_D) = -g_m v_1 \frac{R_D}{1 + g_{ds} R_D}$$

Le courant de grille est nul, c.-à-d.  $i_1 = 0$

On en tire:

tire:

$$A_{v} = \frac{v_{2}}{v_{1}} = \frac{-g_{m}R_{D}}{1 + g_{ds}R_{D}} = -g_{m}\left(R_{D} / / \frac{1}{g_{ds}}\right) \qquad \Rightarrow \qquad si:R_{D} << \frac{1}{g_{ds}} \qquad A_{v} = -g_{m}R_{D}$$

$$si: \qquad \frac{1}{g_{ds}} << R_{D} \qquad A_{v} = -\frac{g_{m}}{g_{ds}}$$

$$A_{i} = \infty \qquad et \qquad R_{in} = \infty$$

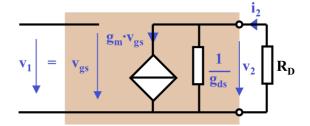

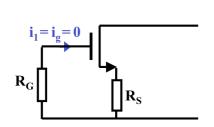

Pour le calcul de la résistance de sortie, le schéma "petits signaux" est le suivant :

$$\begin{aligned} v_{gs} &= v_1 = R_G i_g = 0 \\ i_2 &= g_m v_{gs} + g_{ds} v_2 &=> i_2 = g_{ds} v_2 \\ R_{out} &= \frac{v_2}{i_2} = \frac{1}{g_{ds}} \quad \text{est indépendante de } R_G \end{aligned}$$

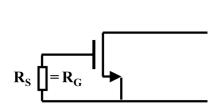

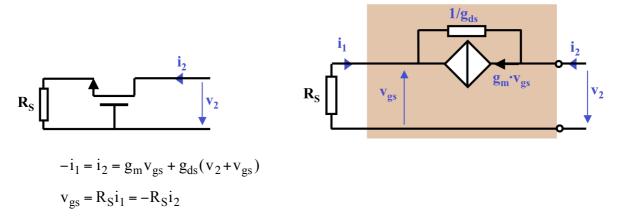

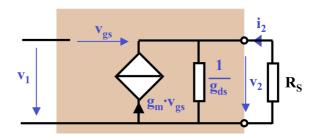

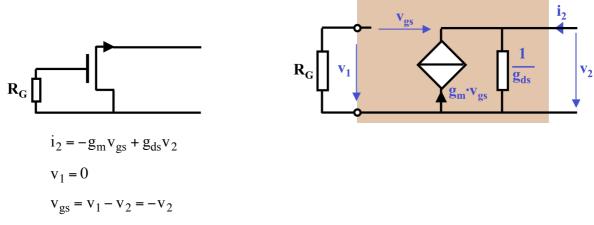

#### 1.4.7 Montage Grille Commune

Dans le schéma "petits signaux", la grille est à la masse, borne commune à l'entrée et à la sortie:

$$\begin{aligned} v_1 &= -v_{gs} \\ i_1 &= -g_m v_{gs} - g_{ds} (v_2 - v_1) = g_m v_1 + g_{ds} (v_1 - v_2) \\ i_2 &= +g_m v_{gs} + g_{ds} (v_2 - v_1) = -g_m v_1 - g_{ds} (v_1 - v_2) \\ v_2 &= -R_D i_2 \end{aligned}$$

De ces équations, on tire:

$$\begin{split} A_v &= \frac{v_2}{v_1} = \frac{(g_m + g_{ds})R_D}{1 + g_{ds}R_D} & R_{in} = \frac{v_1}{i_1} = \frac{1 + g_{ds}R_D}{g_m + g_{ds}} & A_i = \frac{i_2}{i_1} = -1 \\ \\ \Rightarrow & \text{si}: R_D << \frac{1}{g_{ds}} & A_v = (g_m + g_{ds})R_D & \text{et} & R_{in} = \frac{1}{g_m + g_{ds}} \\ \\ \text{si}: & \frac{1}{g_{ds}} << R_D & A_v = \frac{g_m + g_{ds}}{g_{ds}} & \text{et} & R_{in} = \frac{g_{ds}R_D}{g_m + g_{ds}} \end{split}$$

Pour le calcul de la résistance de sortie, le schéma "petits signaux" est le suivant :

$$\begin{split} R_{out} = \frac{v_2}{i_2} = \frac{1}{g_{ds}} \Big[ 1 + (g_m + g_{ds}) R_S \Big] & => \quad \text{si} : R_S << \frac{1}{g_m + g_{ds}} \\ \text{si} : \quad \frac{1}{g_m + g_{ds}} << R_S \quad R_{out} = \frac{(g_m + g_{ds}) R_S}{g_{ds}} \end{split}$$

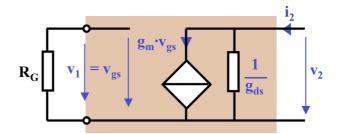

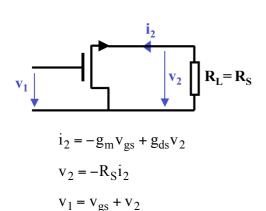

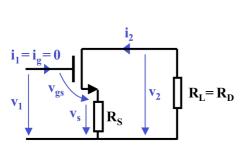

#### 1.4.8 Montage Drain Commun

Dans le schéma "petits signaux", le drain est à la masse, borne commune à l'entrée et à la sortie:

De ces équations, on tire:

$$\begin{split} A_v = & \frac{v_2}{v_1} = \frac{g_m R_S}{1 + (g_m + g_{ds}) R_S} \\ & => \quad si: R_S << \frac{1}{g_{ds}} \\ & si: \quad \frac{1}{g_{ds}} << R_S \quad A_v = \frac{g_m R_S}{1 + g_m R_S} \\ A_i = & \frac{i_2}{i_1} = \infty \quad \text{et} \quad R_{in} = \frac{v_1}{i_1} = \infty \end{split}$$

Pour le calcul de la résistance de sortie, le schéma "petits signaux" est le suivant :

$$R_{out} = \frac{V_2}{i_2} = \frac{1}{g_{m} + g_{ds}}$$

est indépendante de  $R_G$

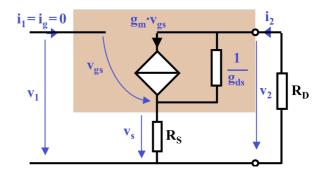

#### 1.4.9 Montage Source Commune Dégénérée

Comme pour la source commune, l'entrée est sur la grille et la sortie au drain. Mais dans le schéma "petits signaux", une résistance entre la source et la masse diminue (dégénère) le gain  $A_v$ .

$$i_2 = g_m v_{gs} + g_{ds}(v_2 - v_s)$$

$$v_2 = -R_D i_2$$

$$v_s = i_2 R_S$$

$$v_1 = v_{gs} + v_s$$

$$\begin{split} A_v &= \frac{v_2}{v_1} = \frac{-g_m R_D}{1 + (g_m + g_{ds}) R_S + g_{ds} R_D} = \frac{-g_m \bigg[ R_D \big/ \big( \frac{1}{g_{ds}} \big[ 1 + (g_m + g_{ds}) R_S \big] \big) \bigg]}{1 + (g_m + g_{ds}) R_S} \\ &=> \quad \text{si}: \ R_D << \frac{1}{g_{ds}} \big[ 1 + (g_m + g_{ds}) R_S \big] \\ &=> \quad \text{si}: \quad \frac{1}{g_{ds}} \big[ 1 + (g_m + g_{ds}) R_S \big] << R_D \\ &=> \quad A_v = \frac{-g_m R_D}{1 + (g_m + g_{ds}) R_S} \\ \\ &=> \quad A_v = \frac{-g_m}{g_{ds}} \bigg[ 1 + (g_m + g_{ds}) R_S \big] << R_D \\ &=> \quad A_v = \frac{-g_m}{g_{ds}} \\ \end{split}$$

Pour le calcul de la résistance de sortie, le schéma "petits signaux" est le suivant :

$$i_2 = g_m v_{gs} + g_{ds} (v_2 - v_s)$$

$v_s = i_2 R_S$

$v_1 = 0 \implies v_{gs} = v_1 - v_s = -v_s$

$$\begin{split} R_{out} = \frac{v_2}{i_2} = \frac{1}{g_{ds}} \Big[ 1 + (g_m + g_{ds}) R_S \Big] & => \quad \text{si} : R_S << \frac{1}{g_m + g_{ds}} \\ \text{si} : \quad \frac{1}{g_m + g_{ds}} << R_S \quad R_{out} = \frac{(g_m + g_{ds}) R_S}{g_{ds}} \end{split}$$

#### 1.5. RESISTANCES AUX ACCES DES TRANSISTORS

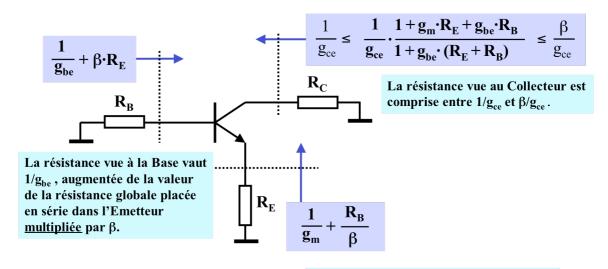

#### 1.5.1 Résumé synthétique des résistances aux accès du transistor bipolaire

Dans des conditions d'utilisation courantes (attention aux limites de validité établies précédemment!), les résultats obtenus peuvent se résumer aux approximations de la figure cidessous :

La résistance vue à l'Emetteur vaut  $1/g_m$ , augmentée de la valeur de la résistance globale placée en série dans la Base divisée par  $\beta$ .

Cette figure donne la résistance entre un accès du transistor et la masse en fonction des paramètres  $g_m$ ,  $g_{be}$  et  $g_{ce}$ , et des résistances de charge des deux autres accès.

Pour rappel, le gain en tension des montages classiques, dans les mêmes conditions:

$$A_{v,EC} = \frac{v_C}{v_B} = \frac{-g_m R_C}{1 + g_{ce} R_C} = -g_m \left( R_C // \frac{1}{g_{ce}} \right)$$

$$A_{v,BC} = \frac{v_C}{v_E} = \frac{g_m R_C}{1 + g_{ce} R_C} = g_m \left( R_C // \frac{1}{g_{ce}} \right)$$

$$A_{v,CC} = \frac{v_E}{v_B} = \frac{g_m R_E}{1 + g_m R_E}$$

tendant vers l'unité lorsque  $R_E > 1/g_m$

$$A_{v,ECd\acute{e}g\acute{e}n\acute{e}r\acute{e}} = \frac{v_{C}}{v_{B}} = \frac{-g_{m}R_{C}}{1 + g_{m}R_{E} + g_{ce}R_{C}(1 + g_{be}R_{E})} = \frac{-g_{m}\left[R_{C} / / \left(\frac{1}{g_{ce}} \cdot \frac{1 + g_{m}R_{E}}{1 + g_{be}R_{E}}\right)\right]}{1 + g_{m}R_{E}}$$

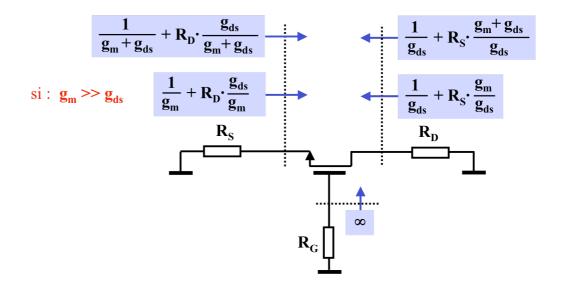

#### 1.5.2 Résumé synthétique des résistances aux accès du transistor MOS

Les résultats obtenus précédemment peuvent être résumés dans la figure ci-dessous :

Cette figure donne la résistance entre un accès du transistor et la masse en fonction des paramètres  $g_m$  et  $g_{ds}$ , et des résistances de charge des deux autres accès.

Pour rappel, le gain en tension des montages classiques, dans les mêmes conditions:

$$\begin{split} A_{v,SC} &= \frac{v_D}{v_G} = \frac{-g_m R_D}{1 + g_{ds} R_D} = -g_m \left( R_D / \! / \frac{1}{g_{ds}} \right) \\ A_{v,GC} &= \frac{v_D}{v_S} = \frac{(g_m + g_{ds}) R_D}{1 + g_{ds} R_D} = (g_m + g_{ds}) \left( R_D / \! / \frac{1}{g_{ds}} \right) \\ A_{v,DC} &= \frac{v_S}{v_G} = \frac{g_m R_S}{1 + (g_m + g_{ds}) R_S} \\ A_{v,SCd\acute{e}g\acute{e}n\acute{e}r\acute{e}e} &= \frac{v_D}{v_G} = \frac{-g_m R_D}{1 + (g_m + g_{ds}) R_S + g_{ds} R_D} = \frac{-g_m \left[ R_D / \! / \left( \frac{1}{g_{ds}} \left[ 1 + (g_m + g_{ds}) R_S \right] \right) \right]}{1 + (g_m + g_{ds}) R_S} \end{split}$$

| L'ampli         | ficateur        | différe | ntiel |

|-----------------|-----------------|---------|-------|

| $\perp u m p u$ | <i>jicaieni</i> | uillele | muci  |

## L'AMPLIFICATEUR DIFFERENTIEL

### 2. L'AMPLIFICATEUR DIFFERENTIEL

|              |                                                                                                 | page     |

|--------------|-------------------------------------------------------------------------------------------------|----------|

| 2.1.         | INTRODUCTION                                                                                    | 3        |

| 2.2.         | SCHEMA ET PRINCIPE DE FONCTIONNEMENT                                                            | 5        |

| 2.3.         | FONCTION DE TRANSFERT "GRANDS SIGNAUX"                                                          | 7        |

| 2.4.         | COMPORTEMENT "PETITS SIGNAUX" DE<br>L'AMPLI DIFFERENTIEL A CHARGES                              | 10       |

| 211          | RESISTIVES Coin on tongion différentiel A 1                                                     | 10       |

|              | Gain en tension différentiel Ad                                                                 | 10       |

|              | Gain en tension différentiel Ad de l'ampli différentiel dégénéré                                | 14       |

| 2.4.3        | Gain en tension de mode commun A <sub>C</sub>                                                   | 16       |

| 244          | Taux de réjection de mode commun                                                                | 10<br>17 |

| <b>2.4.4</b> | Effets d'une charge externe                                                                     | 17       |

| 2.5.         | AMPLI DIFFERENTIEL A CHARGES ACTIVES                                                            | 19       |

| 2.5.1        | Principe des amplificateurs à charge active                                                     | 19       |

| 2.5.2        | Gain en tension différentiel A <sub>d</sub> de l'ampli différentiel à charges actives           | 19       |

| 2.5.3        | Gain en tension de mode commun $A_{c}$ de l'ampli différentiel à charges actives                | 20       |

| 2.5.4        | Variante de l'ampli différentiel à charge active à miroir de                                    |          |

|              | courant                                                                                         | 21       |

| 2.5.5        | Réalisation de miroir de courant en composants discrets                                         | 23       |

| 2.6.         | APPLICATION PARTICULIERE DE<br>L'AMPLIFICATEUR DIFFERENTIEL:                                    |          |

|              | LE MULTIPLIEUR ANALOGIQUE                                                                       | 25       |

| 2.6.1        | Amplificateur différentiel à transconductance variable, multiplieur analogique "deux quadrants" | 25       |

| 2.6.2        | Multiplieur analogique "quatre quadrants" à cellule de "Gilbert"                                | 26       |

| 2.6.3        | Applications du multiplieur analogique à cellule de "Gilbert"                                   | 27       |

#### 2.1. INTRODUCTION

L'amplificateur différentiel de base, encore appelé "paire différentielle", est un montage symétrique, basé sur deux transistors couplés par les émetteurs, pour des bipolaires, ou les sources, pour des MOS. C'est un bloc fonctionnel extrêmement important, utilisé de façon intensive dans les circuits électroniques, en particulier dans les circuits intégrés.

Dans les circuits analogiques, la paire différentielle est utilisée notamment comme étage d'entrée des amplificateurs opérationnels. Elle est à la base du multiplieur analogique à 4 quadrants (cellule de Gilbert). On l'utilise aussi dans certains circuits logiques, en particulier dans la famille ECL.

La paire différentielle est un amplificateur de signaux continus et alternatifs. Le couplage d'entrée est donc direct, sans capacité série, et aucune capacité de découplage n'est nécessaire. Malgré cette propriété, son point de fonctionnement au repos (ou sa polarisation) est très stable, et très peu influencé par la température ou les dispersions des caractéristiques des composants, et son gain en tension est élevé.

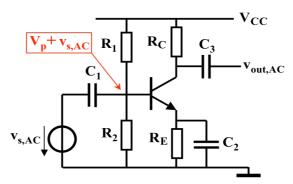

Dans l'amplificateur de signal alternatif (AC) classique ci-dessous, la polarisation  $V_p$  et le signal  $v_{s,AC}$ , sont traités différemment grâce aux capacités de couplage et de découplage.

Pour un amplificateur de petit signal continu (DC), l'utilisation de capacités de couplage et de découplage est exclue.

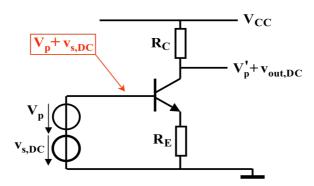

Avec le même principe de polarisation, un schéma possible est le suivant:

Cette solution est inacceptable, car:

- la source de polarisation doit être flottante,

- le point de repos doit être très précis et stable, car toute erreur se confond avec le signal utile DC,

- la sensibilité à la température est importante, puisque toute variation de  $V_{BE}$  (-2 mV/°) entraı̂ne une variation du point de repos qui se confond avec le signal utile DC.

- le gain de l'étage est fortement limité  $|A_v| = R_C/R_E$ .

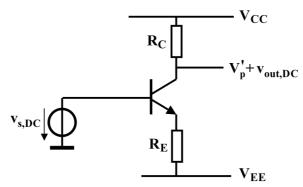

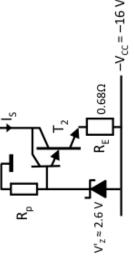

Un autre principe, ne nécessitant pas de source flottante, est une polarisation par une alimentation négative:

Cette solution est également inacceptable, car, à part la suppression de la source de polarisation flottante, les autres défauts subsistent, à savoir:

- l'alimentation  $V_{\text{EE}}$  doit être très précise et stable, car toute erreur se confond avec le signal utile DC,

- la sensibilité à la température est importante, puisque toute variation de  $V_{BE}$  (-2 mV/°) entraîne une variation du point de repos qui se confond avec le signal utile DC,

- le gain de l'étage est fortement limité  $|A_v| = R_C/R_E$ .

La paire différentielle permet de supprimer ces défauts, au prix de quelques composant actifs supplémentaires (au minimum 1).

#### 2.2. SCHEMA ET PRINCIPE DE FONCTIONNEMENT

Un amplificateur différentiel peut être réalisé aussi bien avec des transistors bipolaires que MOS. L'explication qui suit se base sur l'utilisation de transistors bipolaires, mais elle peut immédiatement être transposée pour les transistors MOS.

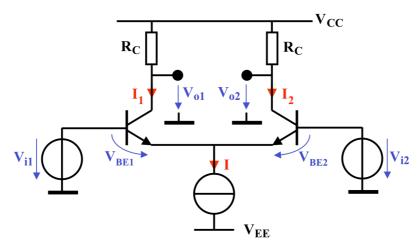

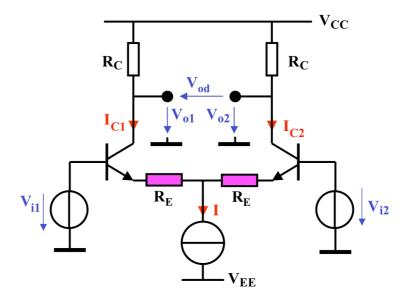

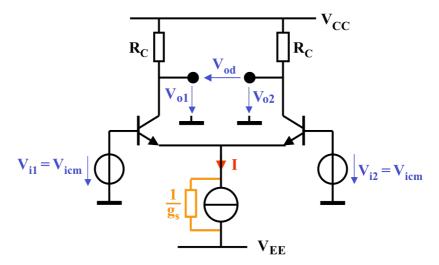

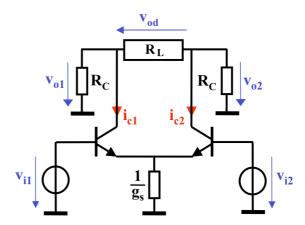

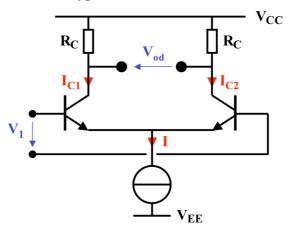

L'amplificateur différentiel de base, ou paire différentielle, est constitué de deux transistors couplés par les émetteurs, et polarisés par une source de courant continu, selon le schéma suivant:

Pour garantir les meilleures performances, les deux transistors doivent, autant que possible, avoir des caractéristiques identiques, et se trouver à la même température. Ces conditions sont quasi-automatiquement remplies en circuits intégrés.

Les deux émetteurs reliés sont au même potentiel d'où :  $V_{i1} - V_{BE1} = V_{i2} - V_{BE2}$

Tant que les deux bases sont au même potentiel  $V_{i1} = V_{i2} = V_{ic}$ , donc que la différence de potentiel entre les bases, dite *signal d'entrée différentiel*, est nulle, alors  $V_{BE1} = V_{BE2}$ , ce qui implique que les deux transistors identiques conduisent des courants égaux, chacun valant donc la moitié du courant constant de la source de polarisation. Par conséquent, les deux collecteurs restent à des potentiels constants et égaux:  $V_{o1} = V_{o2} = V_{CC} - R_C I/2$

On conçoit que <u>la température n'a pas d'influence sur cette situation</u> car la variation thermique de V<sub>BE</sub> affecte de façon identique les deux transistors, ce qui conserve l'équilibre de l'ensemble.

Une variation conjointe du potentiel des deux entrées  $V_{i1} = V_{i2} = V_{ic}$ , dit signal d'entrée de mode commun, ne modifie en rien l'équilibre, tant que ni les transistors ni la source de polarisation n'entrent en saturation.

Lorsqu'on impose une différence de potentiel entre les bases, dit *signal d'entrée différentiel*, on crée un déséquilibre entre les deux branches. Le courant I se répartit dès lors de façon inégale entre les deux transistors, ce qui fait varier le potentiel de chaque collecteur en sens opposé l'un de l'autre. Le signal de sortie peut être recueilli soit entre les deux collecteurs (sortie différentielle), soit entre un des collecteurs et un point fixe, tel que la masse (sortie "single ended" ou asymétrique).

Lorsque la différence de potentiel entre les bases dépasse un certain niveau, l'un des transistors est bloqué, et la totalité du courant I passe par l'autre transistor. A ce moment les potentiels des collecteurs ne changent plus: on peut dire que le signal de sortie "sature", mais cette saturation d'amplitude n'implique pas que le transistor qui conduit passe en mode saturé puisque son courant collecteur est limité à la valeur I, et donc le potentiel minimal de son collecteur est imposé à  $(V_{CC}-R_{C}I)$ .

#### Exemple numérique:

Soit I=2 mA,  $R_C=2.2$  k $\Omega$ , et  $V_{CC}=10$  V. Pour une tension différentielle d'entrée nulle, chaque transistor est parcouru par 1 mA (en négligeant le courant de base), et chaque collecteur se trouve polarisé à 7,8 V. Si on applique une tension différentielle suffisante entre les 2 entrées, un des transistors sera parcouru par un courant nul, ce qui fera remonter son collecteur à 10 V, tandis que l'autre transistor sera parcouru par un courant de 2 mA et verra son collecteur chuter à 5,6 V. Il ne sera pas saturé tant que sa base n'est pas portée au dessus de ces 5.6 V.

En conclusion, <u>l'amplificateur différentiel idéal n'amplifie que la différence de potentiel entre les deux entrées, et n'est pas sensible au potentiel moyen, dit de "mode commun" de celles-ci.</u>

Dans un amplificateur différentiel réel (ou non idéal), la source de courant I peut présenter une conductance de sortie  $g_s$  non nulle. Dans ce cas, un signal d'entrée de mode commun provoque une modification équivalente du potentiel des émetteurs, donc de la tension aux bornes de la source de courant, ce qui modifie légèrement sa valeur. Si le courant I varie, la chute de tension aux bornes des deux collecteurs varie également. Si la sortie de l'ampli se fait en mode différentiel, donc entre les deux collecteurs, l'effet sera nul à condition que les deux transistors soient parfaitement identiques. Par contre, si la sortie se fait entre un des collecteurs et la masse, une variation sera perceptible. Cette imperfection s'appelle le *gain de mode commun*.

#### Exemple numérique:

En reprenant l'exemple précédent avec un conductance  $g_S$  de  $10^{-5}~\Omega^{-1}$ , une tension d'entrée de mode commun de 5 V provoquera une augmentation du courant de polarisation de 50  $\mu A$ , donc 25  $\mu A$  supplémentaires dans chaque transistor, d'où une baisse de potentiel de 55 mV des deux collecteurs .

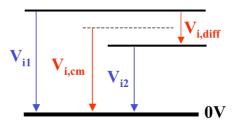

De façon générale, pour des signaux quelconques  $V_{i1}$  et  $V_{i2}$  appliqués aux entrées, on peut toujours définir ceux-ci comme la somme d'un <u>signal d'entrée différentiel</u> et d'un <u>signal d'entrée</u> de mode commun:

• Signal d'entrée de mode commun, appliqué simultanément aux deux entrées:

$$V_{ic} = \frac{V_{i1} + V_{i2}}{2}$$

• <u>Signal d'entrée différentiel</u>, appliqué de façon antisymétrique aux deux entrées (c'està-dire la moitié avec le signe positif à une entrée, et la moitié avec le signe négatif à l'autre entrée):

$$V_{id} = V_{i1} - V_{i2}$$

Lors de l'étude des propriétés de l'ampli différentiel en petits signaux, on étudiera séparément les effets des signaux différentiels et de mode commun. Dans un premier temps, on étudiera seulement <u>l'amplification de mode différentiel</u>, A<sub>d</sub>, c'est à dire l'effet de la composante différentielle du signal d'entrée sur la sortie, en l'absence de signal d'entrée de mode commun. Dans un paragraphe ultérieur, on traitera le cas de <u>l'amplification de mode commun</u>, A<sub>c</sub>, c'est-à-dire l'effet de la composante de mode commun du signal d'entrée sur la sortie. L'effet global s'obtiendra en appliquant le principe de superposition.

#### 2.3. FONCTION DE TRANSFERT "GRANDS SIGNAUX"

L'étude de la fonction de transfert de la paire différentielle pour les signaux de grande amplitude est importante à divers titres:

- elle permet d'illustrer dans quelles limites son comportement pourra être qualifié de "linéaire", et donc quelle sera l'amplitude maximum des "petits signaux" admissibles dans un ampli linéaire;

- elle montre que la tension de sortie n'atteint pas brutalement une limite de saturation, mais tend en douceur vers une amplitude limite sans que les transistors de la paire différentielle n'entre en mode saturé;

- certaines applications font directement usage de cette fonction non linéaire, comme le circuit de conversion d'un signal triangulaire en un signal quasi sinusoïdal.

Dans cette analyse non-linéaire, on admet, comme hypothèse, que la conductance de sortie  $g_S$  de la source de courant, ainsi que celle  $g_{ce}$  (effet Early) des transistors, sont négligeables.

Si les transistors sont identiques (appariement correct) et sont à la même température, on peut admettre que leurs paramètres  $I_s$  et  $\beta$  sont identiques:

$$I_{s1} = I_{s2} = I_{s} \qquad \text{et} \qquad \beta_{1} = \beta_{2} = \beta >> 1$$

$$\begin{matrix} V_{od} \\ V_{od} \end{matrix} \qquad \begin{matrix} V_{od} \\ V_{ol} \end{matrix} \qquad \begin{matrix} V_{od} \\ V_{ol} \end{matrix} \qquad \begin{matrix} V_{od} \\ V_{ol} \end{matrix} \qquad \begin{matrix} V_{bE2} \\ V_{i2} \end{matrix} \qquad \begin{matrix} V_{i2} \\ V_{i2} \end{matrix} \qquad \begin{matrix} V_{i2} \\ V_{i3} \\ V_{i4} \end{matrix} \qquad \begin{matrix} V_{i2} \\ V_{i5} \\ V_{i6} \\ V_{i6} \\ V_{i6} \\ V_{i7} \\ V_{i8} \end{matrix} \qquad \begin{matrix} V_{i1} \\ V_{i1} \\ V_{i2} \\ V_{i1} \\ V_{i2} \\ V_{i2} \\ V_{i3} \\ V_{i4} \\ V_{i5} \\ V_{i5} \\ V_{i6} \\ V_{i6} \\ V_{i7} \\ V_{i8} \\ V_{i8}$$

La tension d'entrée différentielle V<sub>id</sub> peut aisément s'exprimer en fonction des courants de collecteurs par le développement suivant:

$$\begin{split} I_{C1} &= I_s \cdot e^{\frac{V_{BE1}}{U_T}} \quad \Rightarrow \quad V_{BE1} = U_T \cdot \ln \frac{I_{C1}}{I_s} \\ I_{C2} &= I_s \cdot e^{\frac{V_{BE2}}{U_T}} \quad \Rightarrow \quad V_{BE2} = U_T \cdot \ln \frac{I_{C2}}{I_s} \\ V_{id} &= V_{BE1} - V_{BE2} = U_T \cdot \left[ \ln \frac{I_{C1}}{I_s} - \ln \frac{I_{C2}}{I_s} \right] = U_T \cdot \ln \frac{I_{C1}}{I_{C2}} \\ I_{C1} + I_{C2} &\cong I_{E1} + I_{E2} = I \qquad \Rightarrow \qquad I_{C1} = \frac{I}{2} + \Delta I \quad \text{et} \quad I_{C2} = \frac{I}{2} - \Delta I \end{split}$$

$$\begin{split} V_{id} &= U_T \cdot ln \frac{\frac{I}{2} + \Delta I}{\frac{I}{2} - \Delta I} \quad \Rightarrow \quad e^{\frac{V_{id}}{U_T}} = \frac{\frac{I}{2} + \Delta I}{\frac{I}{2} - \Delta I} \\ &\frac{I}{2} + \Delta I = (\frac{I}{2} - \Delta I) \cdot e^{\frac{V_{id}}{U_T}} = \frac{I}{2} \cdot e^{\frac{V_{id}}{U_T}} - \Delta I \cdot e^{\frac{V_{id}}{U_T}} \\ \Delta I \cdot (e^{\frac{V_{id}}{U_T}} + 1) &= \frac{I}{2} \cdot (e^{\frac{V_{id}}{U_T}} - 1) \\ \Delta I &= \frac{I}{2} \cdot \frac{e^{\frac{V_{id}}{U_T}} - 1}{e^{\frac{V_{id}}{U_T}} + 1} \quad \Leftrightarrow \quad \Delta I = \frac{I}{2} \cdot tanh \left(\frac{V_{id}}{2 \cdot U_T}\right) \end{split}$$

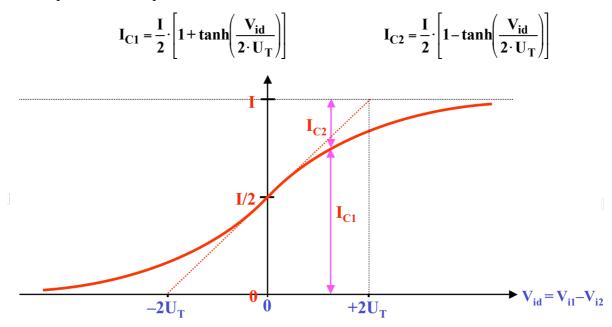

Cette expression de  $\Delta I$  permet d'écrire la valeur des courants de collecteur sous la forme:

Le déséquilibre de courant  $\Delta I$  est donc lié à la tension d'entrée  $V_{id}$  par une loi en tanh. Cette fonction est très linéaire autour de l'origine, puis tend lentement vers la saturation pour des valeurs de  $|V_{id}|$  supérieures à  $U_T$ . Pour une différence des potentiels d'entrée plus grande que 200 mV ( $\approx 8 \cdot U_T$ ), on peut considérer que tout le courant I passe dans l'un ou l'autre des transistors, car tanh(4) = 0.9993.

Les courants de base s'expriment ainsi:

$$I_{B1} = \frac{I}{2 \cdot \beta} \cdot \left[ 1 + \tanh \left( \frac{V_{id}}{2 \cdot U_{T}} \right) \right] \qquad I_{B2} = \frac{I}{2 \cdot \beta} \cdot \left[ 1 - \tanh \left( \frac{V_{id}}{2 \cdot U_{T}} \right) \right]$$

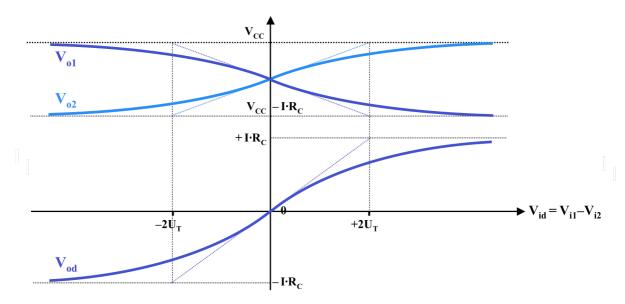

On peut déterminer les potentiels des collecteurs:

$$\begin{aligned} \mathbf{V_{o1}} &= \mathbf{V_{CC}} - \mathbf{R_C} \cdot \mathbf{I_{C1}} = \mathbf{V_{CC}} - \frac{\mathbf{R_C} \cdot \mathbf{I}}{2} - \frac{\mathbf{R_C} \cdot \mathbf{I}}{2} \cdot tanh \bigg( \frac{\mathbf{V_{id}}}{2 \cdot \mathbf{U_T}} \bigg) \\ \\ \mathbf{V_{o2}} &= \mathbf{V_{CC}} - \mathbf{R_C} \cdot \mathbf{I_{C2}} = \mathbf{V_{CC}} - \frac{\mathbf{R_C} \cdot \mathbf{I}}{2} + \frac{\mathbf{R_C} \cdot \mathbf{I}}{2} \cdot tanh \bigg( \frac{\mathbf{V_{id}}}{2 \cdot \mathbf{U_T}} \bigg) \end{aligned}$$

La tension différentielle de sortie est donnée par:

$$\mathbf{V_{od}} = 2 \cdot \mathbf{R_C} \cdot \Delta \mathbf{I} = \mathbf{R_C} \cdot \mathbf{I} \cdot \tanh \left( \frac{\mathbf{V_{id}}}{2 \cdot \mathbf{U_T}} \right)$$

Comme on pouvait s'y attendre, quand  $V_{id}$  est nulle,  $V_{od}$  est également nulle. Il est donc possible de cascader directement plusieurs étages d'amplificateurs différentiels sans provoquer de décalage de la tension de repos de chaque étage.

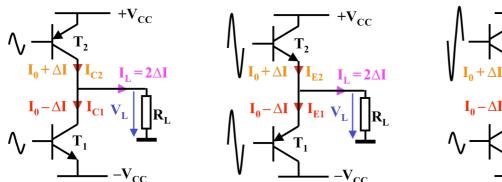

## 2.4. COMPORTEMENT "PETITS SIGNAUX" DE L'AMPLI DIFFERENTIEL A CHARGES RESISTIVES

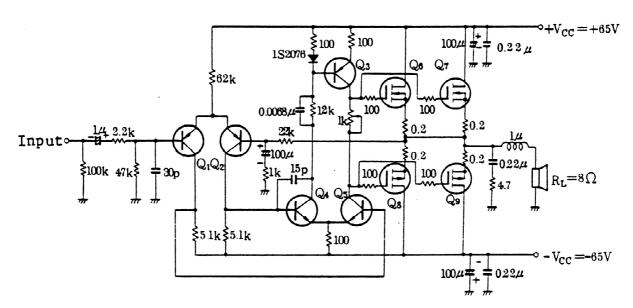

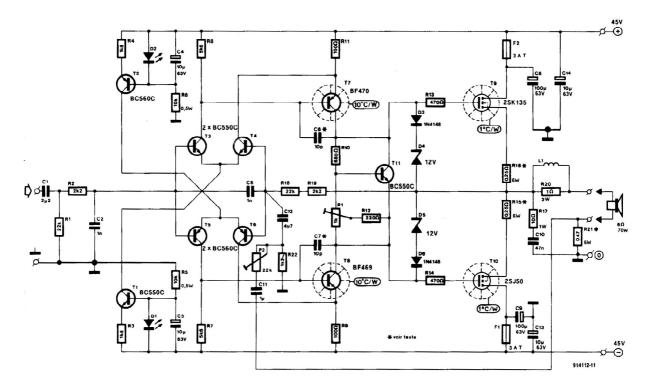

Lorsqu'on réalise un étage amplificateur différentiel à l'aide de composants discrets, on fait généralement usage de simples charges résistives aux collecteurs des deux transistors. Dans le cas d'un amplificateur intégré, les résistances sont souvent (mais pas forcément) remplacées par des charges actives, ce qui sera étudié au point 2.5.

#### 2.4.1 Gain en tension différentiel Ad

Lorsque le signal d'entrée différentiel a une amplitude suffisamment faible, on peut linéariser la fonction de transfert aux environs de l'origine, et ainsi établir l'expression du gain différentiel  $A_d$  de l'ampli différentiel en "petits signaux".

#### Méthode 1: linéarisation de la fonction de transfert "grands signaux"

La fonction de transfert "grands signaux" peut aisément être linéarisée aux environs de l'origine. En effet, le développement de la fonction "tanh(x)" en série de Taylor limitée au premier terme se réduit à son argument "x", d'où:

$$v_{od} = R_C \cdot I \cdot \frac{v_{id}}{2 \cdot U_T}$$

En se rappelant qu'aux environs de l'équilibre, chaque transistor est parcouru par un courant I/2, on voit que l'expression  $(I/2U_T)$  n'est autre que la transconductance  $g_m$  de ces transistors.

$$\mathbf{A_d} = \frac{\mathbf{v_{od}}}{\mathbf{v_{id}}} = \frac{\mathbf{I} \cdot \mathbf{R_C}}{2 \cdot \mathbf{U_T}} = \mathbf{g_m} \cdot \mathbf{R_C} \qquad gain \ en \ mode \ différentielle$$

Le gain (différentiel) de l'ampli différentiel est identique à celui du simple montage émetteur commun. Si la sortie se fait de façon asymétrique (entre un des collecteurs et la masse), la valeur du gain en valeur absolue est divisée par 2, l'un étant positif, l'autre négatif, puisque les deux collecteurs bougent en sens inverse.

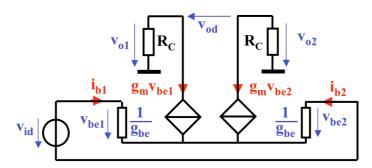

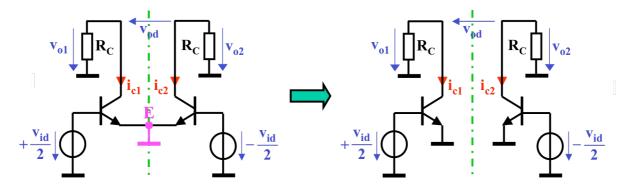

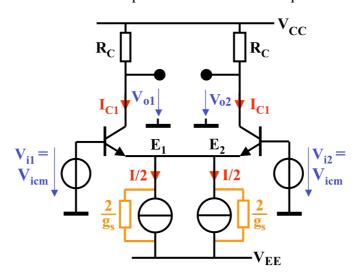

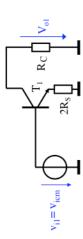

#### Méthode 2: calcul à partir du schéma "petits signaux"

En négligeant la conductance de sortie de la source de courant ainsi que celle  $g_{ce}$  des transistors, le schéma "petits signaux" est le suivant:

$$g_{m} \cdot v_{be1} + g_{be} \cdot v_{be1} + g_{m} \cdot v_{be2} + g_{be} \cdot v_{be2} = 0$$

$g_{m} \cdot v_{be1} + g_{be} \cdot v_{be1} + g_{m} \cdot v_{be2} + g_{be} \cdot v_{be2} = 0$

$$\Rightarrow$$

$v_{be1} = -v_{be2} = \frac{v_{id}}{2}$

$$\begin{split} &v_{o1} = -g_m \cdot v_{be1} \cdot R_C = -g_m \cdot R_C \cdot \frac{v_{id}}{2} \\ &v_{o2} = -g_m \cdot v_{be2} \cdot R_C = -g_m \cdot R_C \cdot \frac{-v_{id}}{2} \\ &v_{od} = v_{o2} - v_{o1} = g_m \cdot R_C \cdot v_{id} \\ &\mathbf{A_d} = \frac{v_{od}}{v_{id}} = \mathbf{g_m} \cdot \mathbf{R_C} \qquad \textit{gain en mode différentielle} \\ &i_{b1} = g_{be} \cdot v_{be1} = g_{be} \cdot \frac{v_{id}}{2} \\ &\mathbf{R_{id}} = \frac{v_{id}}{i_{b1}} = \frac{2}{g_{be}} \qquad \textit{résistance différentielle d'entrée} \end{split}$$

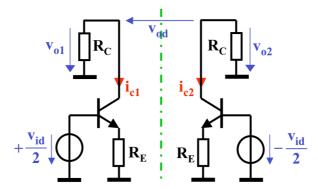

#### Méthode 3: méthode du "demi circuit équivalent"

L'amplificateur différentiel appartient à une classe particulière de circuits: celle des circuits symétriques. Dans ce cas, il est possible d'analyser les propriétés du circuit en petits signaux en utilisant le concept de "demi circuit équivalent". Ce concept permet d'obtenir le résultat en analysant seulement le comportement de la moitié du circuit.

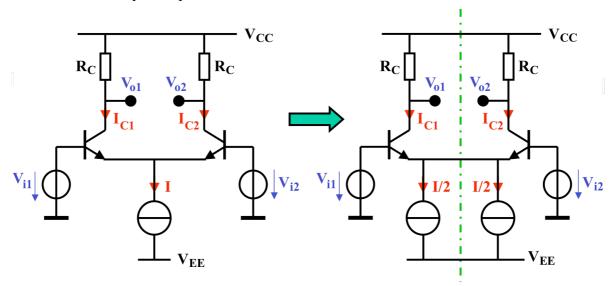

L'idée est la suivante: on commence par remplacer la source de courant par deux sources de courant de valeur moitié, ce qui ne change absolument rien au fonctionnement du circuit, mais le rend totalement symétrique:

Si le circuit est excité par une tension purement différentielle  $v_{id}$ , donc sans composante de mode commun, les deux entrées voient des signaux opposés tels que  $v_{i1} = -v_{i2} = v_{id}/2$ .

Le comportement de la jonction émetteur-base étant linéarisé pour les petits signaux considérés, on voit que le point commun aux deux émetteurs reste à un potentiel constant, puisque les deux bases bougent symétriquement par rapport à la masse.

Dans un circuit équivalent "petits signaux", valable comme on l'a vu jusqu'à présent pour les variations de faible amplitude aux environs du point de fonctionnement, un point dont le potentiel est constant est équivalent à la masse. Dans le cas de l'ampli différentiel, le point de connexion des deux émetteurs est donc l'équivalent d'une masse virtuelle.

Toutes les autres règles habituelles pour le dessin du circuit équivalent "petits signaux" sont applicables, à savoir que les sources de tension constante sont annulées (et donc remplacées par des courts-circuits), et que les sources de courant constant sont également annulées (et donc remplacées par des circuits ouverts).

Le circuit équivalent "petits signaux" valable pour l'étude du gain différentiel peut donc se dessiner comme ci-dessous. Le point commun des émetteurs étant à la masse dans ce circuit équivalent, on ne change en rien son comportement si on le coupe en deux selon l'axe de symétrie, pour étudier séparément chacune des parties. D'où le demi circuit équivalent en mode différentiel résultant.

Le gain en tension d'une moitié de l'ampli différentiel est donc égal au gain d'un montage émetteur commun, soit  $-g_m \cdot R_C$ . En considérant l'ampli différentiel complet, l'écart de tension entre les deux entrées est doublé, ainsi qu'entre les deux sorties. On obtient donc aussi:

$$\begin{aligned} \mathbf{A_d} &= \frac{\mathbf{v_{od}}}{\mathbf{v_{id}}} = \mathbf{g_m} \cdot \mathbf{R_C} & \textit{gain en mode différentielle} \\ \mathbf{R_{id}} &= \frac{\mathbf{v_{id}}}{\mathbf{i_b}} = \frac{2}{\mathbf{g_{be}}} & \textit{résistance différentielle d'entrée} \end{aligned}$$

Cette résistance d'entrée est le double de celle d'un montage émetteur commun qui serait polarisé par un courant I/2.

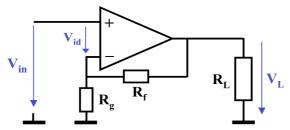

#### Méthode 4: méthode de l'entrée asymétrique

Le gain différentiel ne se modifie pas si on change le niveau moyen des deux entrées. Au lieu d'appliquer la tension différentielle d'entrée  $v_{id}$  de façon antisymétrique, on va dès lors fixer la référence du zéro d'un côté de la source  $v_{id}$ , ce qui revient à connecter une des entrées à la masse et à appliquer la totalité de la tension  $v_{id}$  sur l'autre entrée.

Pour étudier le gain différentiel, on examine successivement l'effet du signal d'entrée de  $T_1$  sur le collecteur de  $T_1$ , puis sur le collecteur de  $T_2$ .

En considérant tout d'abord la sortie sur le collecteur de  $T_1$ , ce transistor se comporte comme un montage émetteur commun dégénéré par la présence d'une résistance entre son émetteur et la masse, qui n'est autre que la résistance d'entrée de  $T_2$  monté en base commune, valant  $1/g_m$ . La tension de sortie  $v_{o1}$  peut dès lors se calculer aisément en se basant sur la formule du gain en tension d'un émetteur commun dégénéré:

$$v_{o1} = \frac{-g_{m} \cdot R_{C}}{1 + g_{m} \cdot R_{E}} \cdot v_{id} = \frac{-g_{m} \cdot R_{C}}{1 + g_{m} \cdot 1/g_{m}} \cdot v_{id} = \frac{-g_{m} \cdot R_{C}}{2} \cdot v_{id}$$

En considérant d'autre part la sortie vers  $T_2$  via l'émetteur de  $T_1$ , on voit que  $T_1$  joue le rôle d'un collecteur commun, suivi d'un transistor  $T_2$  monté en base commune.

$$v_{o2} = \frac{g_m \cdot R_E}{1 + g_m \cdot R_E} \cdot g_m \cdot R_C \cdot v_{id} = \frac{g_m \cdot 1/g_m}{1 + g_m \cdot 1/g_m} \cdot g_m \cdot R_C \cdot v_{id} = \frac{g_m \cdot R_C}{2} \cdot v_{id}$$

Sachant que  $v_{od} = v_{o2} - v_{o1}$ , on obtient:

$$A_d = \frac{v_{od}}{v_{id}} = g_m \cdot R_C$$

gain en mode différentiel à sortie différentielle

La résistance d'entrée différentielle n'est autre que celle d'entrée de T<sub>1</sub>:

$$\mathbf{R_{id}} = \frac{1}{g_{be}} + \beta \cdot \mathbf{R_E} = \frac{1}{g_{be}} + \beta \cdot \frac{1}{g_m} = \frac{2}{g_{be}}$$

résistance différentielle d'entrée

Cette troisième méthode de calcul donne accès à un résultat supplémentaire intéressant. Elle permet en effet de visualiser clairement l'effet d'une conductance non nulle de la source de courant sur le gain différentiel.

Au cas où l'admittance interne de la source de courant aurait une valeur g<sub>s</sub> non nulle, le circuit se transforme comme suit:

Cette admittance se retrouve en parallèle sur l'admittance d'entrée de  $T_2$ , c'est à dire  $g_m$ . Tant que  $g_s$  reste d'un ordre de grandeur inférieure à  $g_m$ , elle ne modifie donc pas les performances du circuit sur le plan du gain différentiel et de la résistance d'entrée différentielle. On verra ultérieurement que  $g_s$  affecte essentiellement le gain en mode commun de l'ampli différentiel.

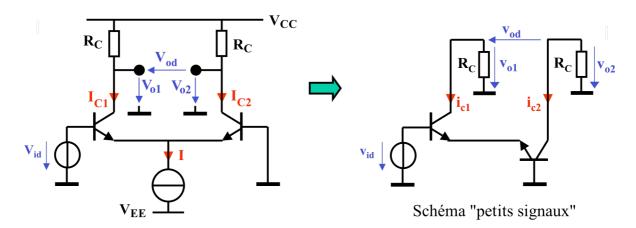

#### 2.4.2 Gain en tension différentiel Ad de l'ampli différentiel dégénéré

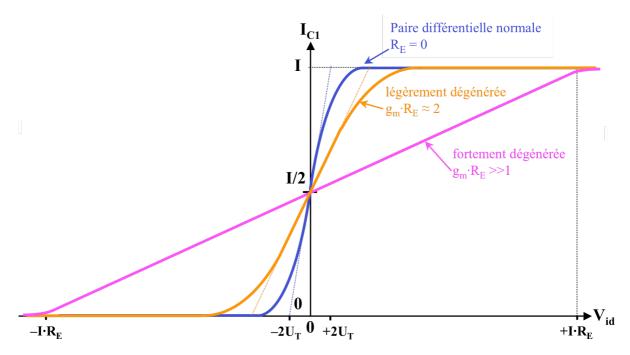

On parle d'ampli différentiel dégénéré lorsque le gain en tension est réduit par l'adjonction de résistances en série dans les émetteurs des deux transistors.

Cette technique permet un contrôle précis de la valeur du gain différentiel. Elle permet également d'augmenter considérablement la gamme des tensions d'entrée pour laquelle la paire différentielle peut être considérée comme linéaire.

La fonction de transfert "grands signaux" répond à l'équation:

$$V_{id} = 2 \cdot U_T \cdot \tanh^{-1} \left( \frac{2 \cdot \Delta I}{I} \right) + 2 \cdot R_E \cdot \Delta I$$

Elle a l'allure suivante:

Le demi circuit équivalent en mode différentiel pour les petits signaux est le suivant:

Le gain en tension différentiel de la paire différentielle dégénérée s'obtient aisément à partir de l'expression du gain en tension du montage EC dégénéré, avec  $R_C << 1/g_{ce}$ :

$$\mathbf{A_d} = \frac{\mathbf{v_{od}}}{\mathbf{v_{id}}} = \frac{\mathbf{g_m} \cdot \mathbf{R_C}}{1 + \mathbf{g_m} \cdot \mathbf{R_E}}$$

gain en mode différentielle à sortie différentielle

Si la paire différentielle est fortement dégénérée, c'est à dire si:

$$g_m \cdot R_E >> 1 \quad \Leftrightarrow \quad I \cdot R_E >> 2 \cdot U_T$$

alors:

$$\mathbf{A_d} = \frac{\mathbf{v_{od}}}{\mathbf{v_{id}}} = \frac{\mathbf{R_C}}{\mathbf{R_E}}$$

gain en mode différentielle

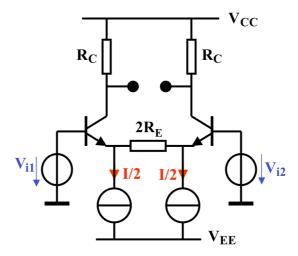

Remarque: la paire différentielle dégénérée, avec le même comportement tel que décrit cidessus, peut aussi se réaliser sous la forme suivante:

Dans ce montage, la résistance d'émetteur n'est parcourue que par le courant différentiel résultant de l'application d'un signal différentiel à l'entrée. Ceci représente un avantage par rapport au schéma classique à une seule source de courant, où les résistances  $R_{\rm E}$  sont parcourues en plus par le courant de polarisation I/2, ce qui réduit la dynamique d'entrée de mode commun.

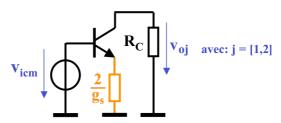

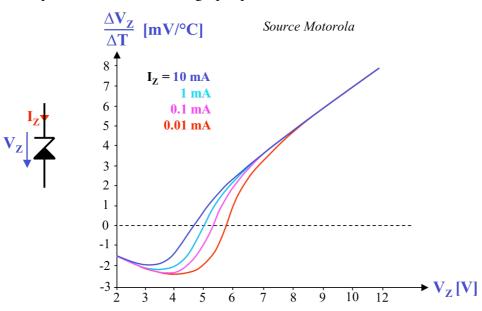

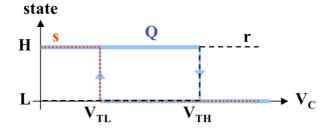

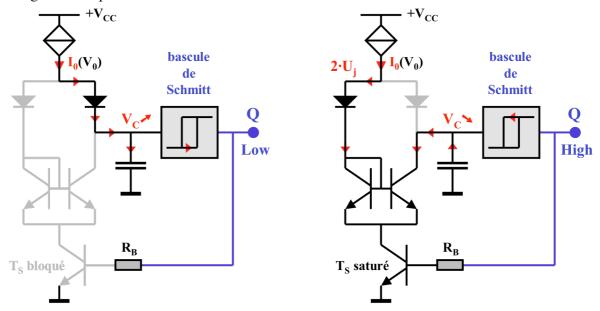

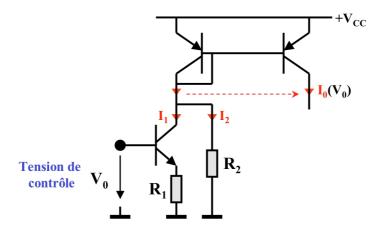

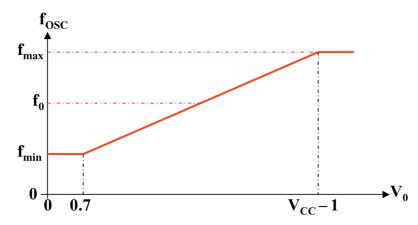

## 2.4.3 Gain en tension de mode commun $A_c$ Taux de réjection de mode commun

Le gain de mode commun est une imperfection des amplis différentiels, que l'on s'efforce de minimiser. Il résulte du fait que les sorties de l'ampli ne sont pas totalement insensibles à l'application d'un même signal sur les deux entrées. Contrairement au cas du gain différentiel, l'admittance parasite g<sub>s</sub> de la source de courant ne peut plus être négligée pour l'étude du gain de mode commun, car c'est précisément cette admittance qui en est la cause principale.

Pour étudier le gain de mode commun, on applique un signal identique sur les 2 entrées:

Le principe d'un demi circuit équivalent peut à nouveau être appliqué pour l'étude du gain de mode commun.

**Attention! :** en mode commun, on attaque l'ampli avec 2 signaux identiques, et le demi circuit équivalent correspondant n'est pas le même qu'en mode différentiel.

Le circuit ci-dessus est tout d'abord représenté sous la forme équivalente suivante:

Lorsque les deux entrées d'un circuit symétrique sont excitées par un même signal, en l'occurrence une tension appelée "tension de mode commun"  $V_{icm}$ , les courants et les tensions dans le circuit ne sont pas perturbés si les branches joignant les deux parties symétriques du circuit sont coupées. Dans ce cas, les deux segments de la connexion d'émetteurs coupée sont simplement laissés flottants, et ne sont donc pas reliés à la masse, car leur potentiel se modifie

avec le signal d'entrée V<sub>icm</sub>. En mode commun, aucun courant ne circule dans les branches reliant les deux parties symétriques, ce qui autorise la coupure effectuée.

Le comportement de la paire différentielle soumise à un signal de mode commun peut donc s'étudier sur le demi circuit équivalent, c'est à dire une seule des deux moitiés identiques.

Pour l'étude du gain en "petits signaux", on annule les sources constantes, ce qui donne le circuit équivalent suivant:

Le gain de mode commun  $A_c$  se définit comme le rapport entre les variations de la tension collecteur et la variation de la tension commune appliquée aux deux entrées de l'ampli différentiel. C'est le gain en tension d'un EC fortement dégénéré, car  $g_s$  est toujours  $<< g_m$ .

$$A_c = \frac{V_{01/2}}{V_{icm}} = -\frac{R_C}{2/g_s} = -\frac{g_s \cdot R_C}{2}$$

Pour réduire le gain de mode commun, on a donc intérêt à utiliser une "bonne" source de courant, avec une conductance de sortie g<sub>s</sub> très faible.

Il faut noter que lorsque les 2 transistors sont identiques, comme on l'a supposé jusqu'ici, le gain de mode commun n'existe que pour une sortie asymétrique de l'ampli différentiel (sortie entre un des collecteurs et la masse).

Pour une sortie différentielle, le gain de mode commun est nul si les composants sont parfaitement appairés, car les deux branches symétriques se comportent de façon identique.

<u>Le taux de réjection du mode commun</u> (Common Mode Rejection Ratio ou CMRR) se définit finalement comme le rapport entre le gain différentiel et le gain de mode commun:

$$CMRR = \frac{\left| A_{d} \right|}{\left| A_{c} \right|} \qquad \text{ou} \qquad CMRR \left[ dB \right] = 20 \cdot log \frac{\left| A_{d} \right|}{\left| A_{c} \right|} = A_{d} \left[ dB \right] - A_{c} \left[ dB \right]$$

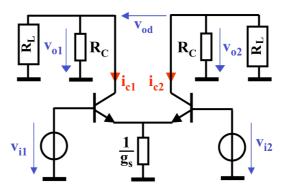

#### 2.4.4 Effets d'une charge externe

Du point de vue "petits signaux", tout ce qui est connecté aux sorties de l'ampli différentiel peut être modélisé par une résistance de charge.

Dans le cas de charges asymétriques, les charges sont entre chaque collecteur et la masse:

Dans les expressions des gains, tant différentiel que de mode commun,  $R_{\rm C}$  est remplacée par  $R_{\rm C}/\!/\,R_{\rm L}$  .

Dans le cas d'une charge symétrique, placée entre les collecteurs:

En mode différentiel, par symétrie, dans un schéma "petits signaux", tout se passe comme si le point milieu de  $R_L$  était à la masse, ce qui revient à avoir deux charges asymétriques de valeur  $R_L/2$ . Dans l'expression du gain différentiel,  $R_C$  est remplacée par  $R_C//(R_L/2)$ .

En mode commun, les deux collecteurs bougent de manière identique et  $R_L$  n'a donc aucun effet sur le gain de mode commun.

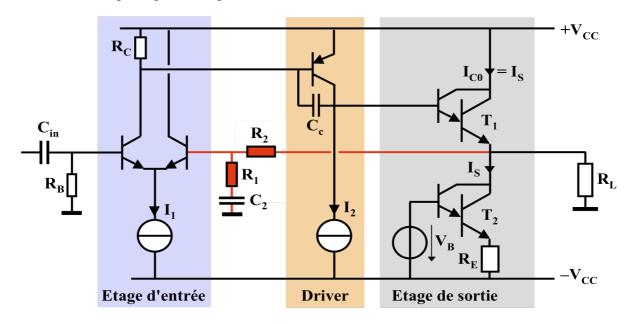

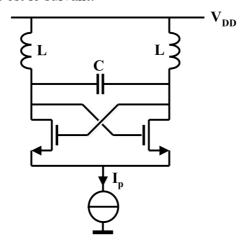

#### 2.5. AMPLI DIFFERENTIEL A CHARGES ACTIVES

#### 2.5.1 Principe des amplificateurs à charge active

Que ce soit pour le simple montage émetteur commun ou pour l'ampli différentiel, on sait que le gain en tension dépend directement de la valeur de la résistance de charge R<sub>C</sub>. L'usage d'une résistance de valeur élevée exigerait aussi une tension d'alimentation de valeur élevée en raison de la chute de tension provoquée par le courant de polarisation. Dans les circuits intégrés, la tension d'alimentation maximum est imposée par la technologie, et il n'est pas économique de réaliser des résistances de valeur élevée.

Pour contourner ces limitations, on peut utiliser le principe de la <u>charge active</u>. Cette technique consiste à remplacer la résistance de charge par une source de courant. Sur le plan de la polarisation, la source de courant fournit le courant de collecteur désiré. Pour les petits signaux variables superposés à la polarisation, cette charge se comporte comme une résistance de valeur très élevée, correspondant à la résistance de sortie de la source de courant.

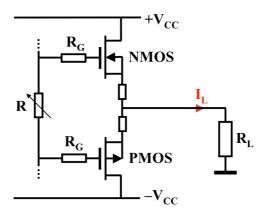

Ce principe est fréquemment appliqué à la paire différentielle intégrée. En prenant certaines précautions, dont il sera question plus loin, il peut aussi être appliqué aux circuits à composants discrets. Le schéma de principe est le suivant:

Ce schéma est utilisé principalement pour une sortie différentielle. Lorsqu'on souhaite utiliser une sortie asymétrique, c'est-à-dire entre un des collecteurs et la masse, on verra qu'il est possible de modifier légèrement la connexion des transistors réalisant les charges actives pour améliorer considérablement les performances.

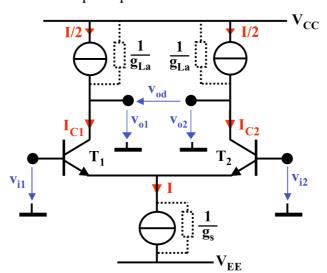

#### 2.5.2 Gain en tension différentiel Ad de l'ampli différentiel à charges actives

Lorsque la résistance équivalente de la charge de collecteur est comparable ou supérieure à  $1/g_{ce}$ , il n'est plus possible de négliger cette dernière.

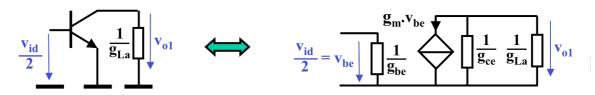

Pour les "petits signaux", le demi circuit équivalent en mode différentiel de l'ampli avec charges actives est le suivant:

Le gain différentiel est égal (en valeur absolue) à celui de l'émetteur commun, et vaut:

$$\mathbf{A_d} = \frac{\mathbf{v_{od}}}{\mathbf{v_{id}}} = \mathbf{g_m} \cdot \frac{1}{\mathbf{g_{ce}} + \mathbf{g_{La}}}$$

gain en mode différentiel à sortie différentielle

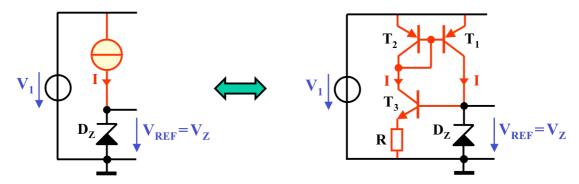

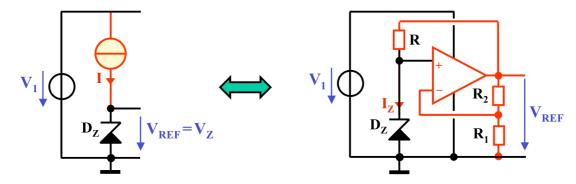

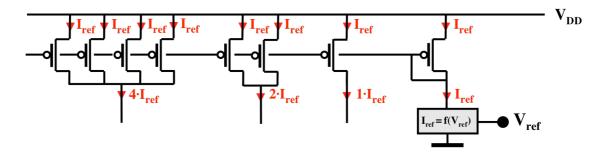

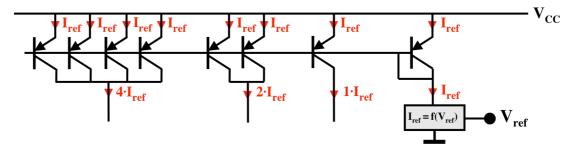

La réalisation pratique des sources de courant se fait à l'aide de miroirs de courant, ainsi:

Ce type de circuit a un gain extrêmement élevé. Il est toutefois délicat à utiliser car son point de fonctionnement au repos dépend de l'équilibre précis des sources de courant du bas et du haut, qui est notamment influencé par la tension de mode commun appliquée aux entrées. Le "gain de mode commun" est en effet particulièrement élevé, comme démontré ci-dessous.

## 2.5.3 Gain en tension de mode commun A<sub>c</sub> de l'ampli différentiel à charges actives

Pour les "petits signaux", le demi circuit équivalent en mode commun de l'ampli avec charges actives est le suivant:

Le "gain de mode commun" est identique à celui d'un EC fortement dégénéré:

$$A_c = \frac{v_{o1/2}}{v_{icm}} \approx -\frac{1/g_{La}}{2/g_s} = -\frac{g_s}{2 \cdot g_{La}}$$

Le "gain de mode commun" est particulièrement élevé en raison de la forte résistance de la charge active. Si les paires  $T_1$ - $T_3$  et  $T_2$ - $T_4$  sont parfaitement identiques, le gain de mode commun n'existe pas pour une sortie différentielle. Toutefois, la dérive du point de fonctionnement peut être suffisamment grande pour réduire considérablement la dynamique de sortie du signal utile, voire même saturer l'un des transistors  $T_1$  à  $T_4$ .

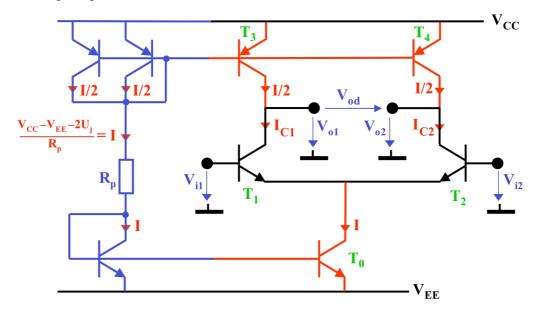

#### 2.5.4 Variante de l'ampli différentiel à charge active à miroir de courant

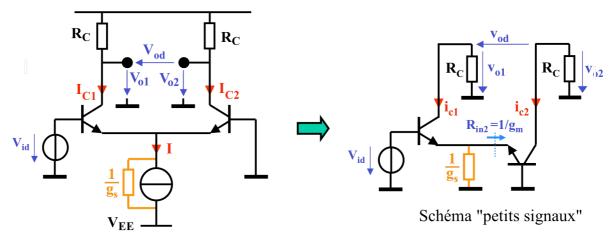

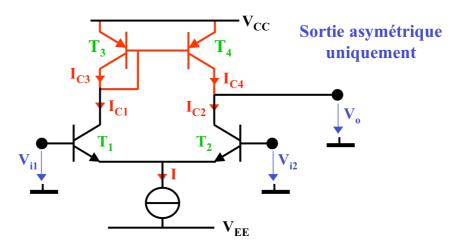

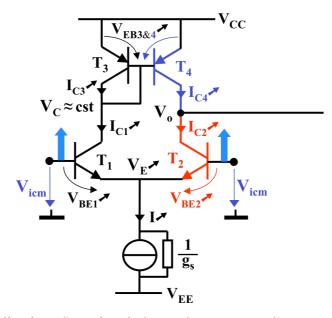

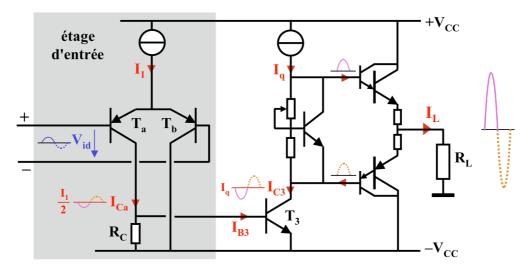

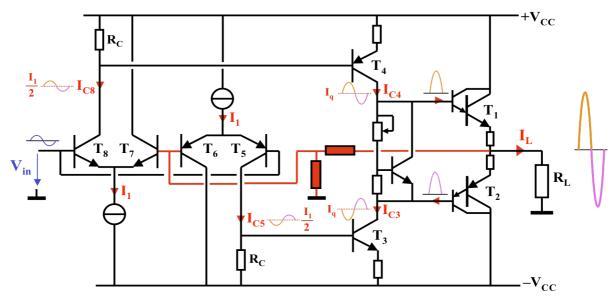

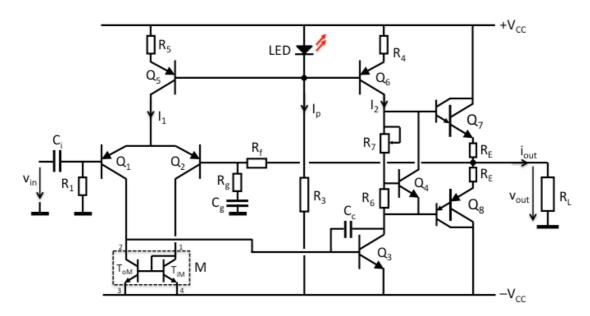

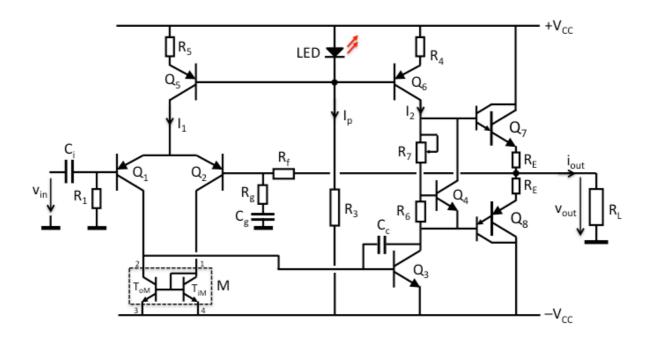

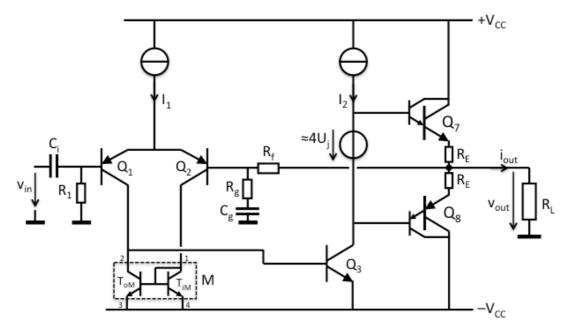

Lorsque seule une sortie asymétrique est désirée, on adopte généralement le schéma suivant:

Dans ce circuit, la paire  $T_3$ - $T_4$  joue le rôle de miroir de courant,  $T_4$  étant la charge active de  $T_2$ . Cette configuration permet notamment de doubler le gain en tension ou la transconductance pour une sortie asymétrique.

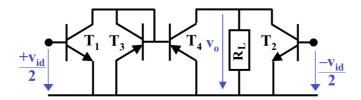

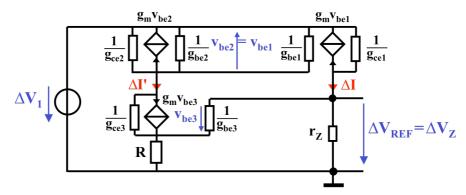

En mode différentiel  $v_{i1} = -v_{i2} = v_{id}/2$ , on peut considérer que pour les "petits signaux" les émetteurs sont à la masse. Le schéma "petits signaux", avec une éventuelle charge  $R_L$  extérieure en sortie, est alors le suivant:

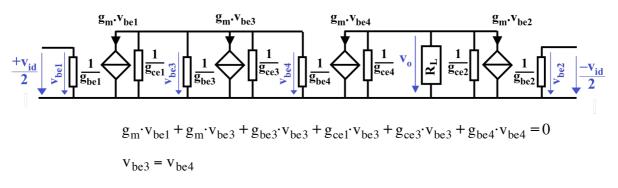

Avec le schéma équivalent détaillé des transistors, tous parcourus par le même courant de repos I/2, donc ayant tous le même  $g_m$ , cela donne:

Comme  $g_m \gg g_{be} \gg g_{ce}$ , on en tire:

$$\begin{split} v_{be3} &= v_{be4} = -v_{be1} \\ v_o &= -(g_m \cdot v_{be4} + g_m \cdot v_{be2}) \cdot \frac{1}{g_{ce2} + g_{ce4} + G_L} \\ v_o &= g_m \cdot (v_{be1} - v_{be2}) \cdot \frac{1}{g_{ce2} + g_{ce4} + 1/R_L} = g_m \cdot v_{id} \cdot \frac{1}{g_{ce2} + g_{ce4} + 1/R_L} \end{split}$$

$$\begin{aligned} \mathbf{A_d} &= \frac{\mathbf{v_0}}{\mathbf{v_{id}}} = \frac{\mathbf{g_m}}{\mathbf{g_{ce2} + g_{ce4}} + 1/R_L} & \textit{gain en mode différentiel à sortie asymétrique !} \\ &\text{si: } R_L << \frac{1}{g_{ce2} + g_{ce4}} & \text{alors: } \mathbf{A_d} = \mathbf{g_m} \cdot \mathbf{R_L} \\ &\text{si: } \frac{1}{g_{ce2} + g_{ce4}} << R_L & \text{alors: } \mathbf{A_{d,max}} = \frac{\mathbf{g_m}}{\mathbf{g_{ce2} + g_{ce4}}} \end{aligned}$$

Malgré son unique sortie asymétrique, la paire différentielle à charge active par miroir de courant a un gain différentiel égal à celui à sortie différentielle de la paire différentielle classique à charges actives par sources de courant, alors que cette dernière voit son gain différentiel diminué de moitié lorsqu'on l'utilise avec une sortie asymétrique.

En tenant compte du fait que le miroir de courant peut être plus sophistiqué, avec une résistance de sortie plus élevée que  $1/g_{ce4}$ , on peut écrire plus généralement:

$$A_d = \frac{v_o}{v_{id}} = \frac{g_m}{g_{ce2} + g_{out,miroir} + \frac{1}{R_L}} = g_m \left(\frac{1}{g_{ce2}} // R_{out,miroir} // R_L\right)$$

Une autre propriété avantageuse de cette paire différentielle avec charge active à miroir de courant est sa faible sensibilité à la tension d'entrée de mode commun.

En effet, lors de l'application d'un signal de mode commun, l'augmentation éventuelle du courant débité par la source se retrouve répartie de façon égale entre les deux transistors  $T_1$  et  $T_2$ . L'augmentation du courant collecteur de  $T_1$  traverse  $T_3$ , est recopiée par  $T_4$  et vient compenser celle dans  $T_2$ . Ce système permet donc de garder l'équilibre. Le potentiel  $V_0$  ne bouge pas. L'étude détaillée du gain de mode commun de cet étage sort toutefois du cadre de ce cours, et est traitée dans le cours de conception des circuits intégrés analogiques.

#### 2.5.5 Réalisation de miroir de courant en composants discrets

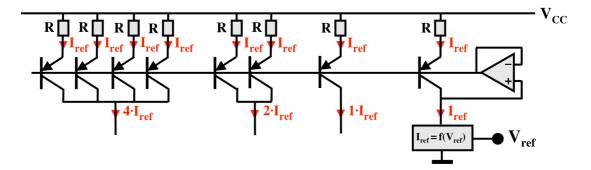

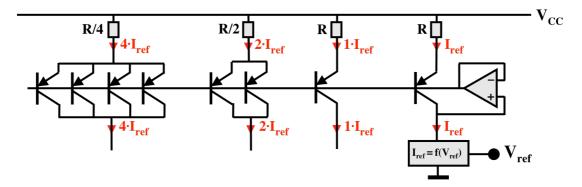

Un miroir de courant intégré jouit d'une excellente précision en raison de l'appariement quasiidéal des transistors qui le composent. Le courant dans les deux branches est donc pratiquement identique.

Sachant que le gain en courant des transistors est grand (facilement plus de 100):

$$\frac{I_2}{I_1} = \frac{I_{C2}}{I_{C1} + I_{B1} + I_{B2}} \cong \frac{I_{C2}}{I_{C1}} = \frac{I_{s2} \cdot e^{V_{BE}/U_T}}{I_{s1} \cdot e^{V_{BE}/U_T}} = \frac{I_{s2}}{I_{s1}} \cong 1$$

Dans le cas d'une réalisation en composants discrets, les différences entre composants se répercutent directement sur la précision. Pour une différence de 10% entre  $I_{s1}$  et  $I_{s2}$ , on observera donc directement la même différence entre les courants des collecteurs.

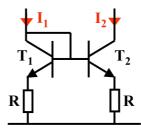

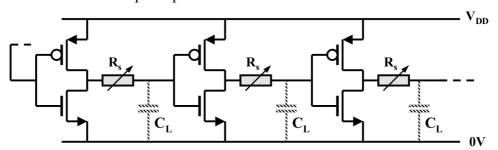

L'ajout d'une petite résistance en série dans la connexion des deux émetteurs permet de réduire considérablement cet écart:

Sachant que le gain en courant des transistors est grand (facilement plus de 100):

$$V_{BE1} + I_1 \cdot R = V_{BE2} + I_2 \cdot R$$

$$I_2 = I_1 + \frac{1}{R} \cdot (V_{BE1} - V_{BE2}) = I_1 + \frac{1}{R} \cdot (U_T \cdot ln \frac{I_1}{I_{s1}} - U_T \cdot ln \frac{I_2}{I_{s2}}) = I_1 + \frac{1}{R} \cdot U_T \cdot ln \frac{I_1}{I_2}$$

Cette équation transcendante doit être résolue par approximations successives.

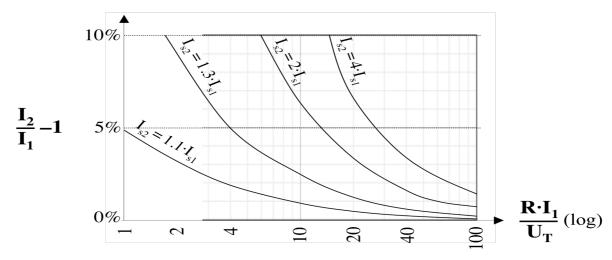

La figure ci-dessous montre l'amélioration de la symétrie obtenue en fonction de la chute de tension sur les résistances:

Exemple numérique:

Pour  $I_1 = 1$  mA, R = 1 k $\Omega$ , et un écart de 10% entre  $I_{s1}$  et  $I_{s2}$ , on trouve  $I_2 = 1.0025$  mA.

La présence des résistances a aussi comme avantage d'augmenter la résistance de sortie d'un facteur  $g_m R$ .

Si:

$$I \cdot R >> U_T$$

alors  $R_{out} = \frac{1}{g_{ce}} \cdot g_m \cdot R = \frac{1}{g_{ce}} \cdot \frac{I \cdot R}{U_T}$

Par contre la dynamique de tension de sortie est réduite de I·R.

#### 2.6. APPLICATION PARTICULIERE DE L'AMPLIFICATEUR DIFFERENTIEL: LE MULTIPLIEUR ANALOGIQUE

Comme l'indique son nom, l'amplificateur différentiel est principalement utilisé pour faire de l'amplification. Une autre application remarquable de cette structure est la multiplication de deux signaux analogiques.

## 2.6.1 Amplificateur différentiel à transconductance variable, multiplieur analogique "deux quadrants"

On a démontré (§2.3.) que l'amplificateur différentiel de base, représenté ci-dessous, avait la caractéristique de transfert suivante:

$$V_{od} = 2 \cdot R_C \cdot \Delta I = R_C \cdot I \cdot \tanh\left(\frac{V_1}{2 \cdot U_T}\right)$$

Pour des signaux  $V_1$  limités à  $\pm$  10 mV autour de zéro, l'approximation linéaire suivante présente une erreur maximum de 1% :

$$V_{od} = R_C \cdot I \cdot \frac{V_1}{2 \cdot U_T}$$

On a donc une multiplication de V<sub>1</sub> par I.

Pour obtenir le produit de deux tensions  $V_1$  et  $V_2$ , il suffit de remplacer la source de courant constant par une source de courant commandée par la seconde tension d'entrée  $V_2$ , selon une relation linéaire, telle que  $I = G \cdot V_2$ .

Ce qui donnera finalement:

$$\mathbf{V_{od}} = \mathbf{R_C} \cdot \mathbf{G} \cdot \mathbf{V_2} \cdot \frac{\mathbf{V_1}}{2 \cdot \mathbf{U_T}} = \frac{\mathbf{R_C} \cdot \mathbf{G}}{2 \cdot \mathbf{U_T}} \cdot \mathbf{V_1} \cdot \mathbf{V_2}$$

Ce multiplicateur est dit "deux quadrants" (dans un plan  $V_1,V_2$ ) car, si  $V_1$  peut être positif ou négatif,  $G \cdot V_2$  doit toujours être positif, donc  $V_2$  d'une seule polarité.

Le nom d'amplificateur différentiel à transconductance variable, vient du fait que  $V_2$  fait varier le courant I, donc la transconductance  $g_m = I/2U_T$  des transistors.

#### 2.6.2 Multiplieur analogique "quatre quadrants" à cellule de "Gilbert"

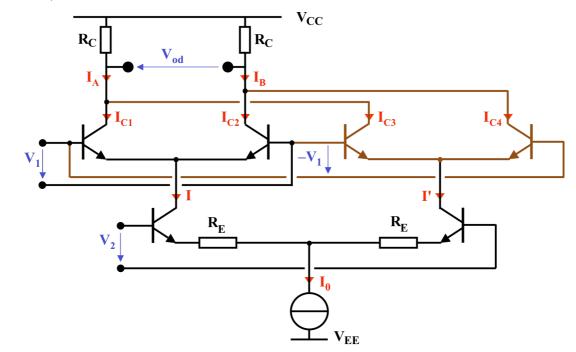

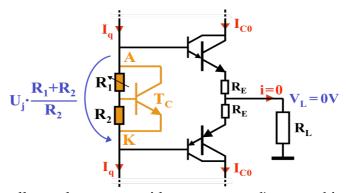

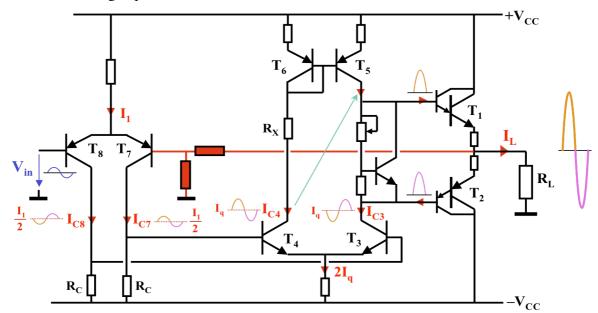

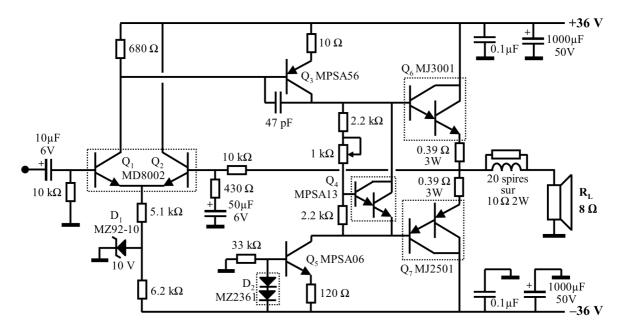

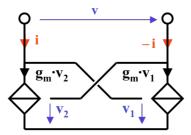

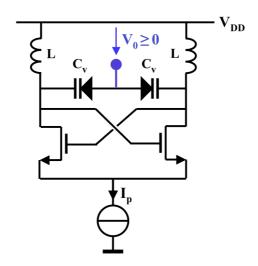

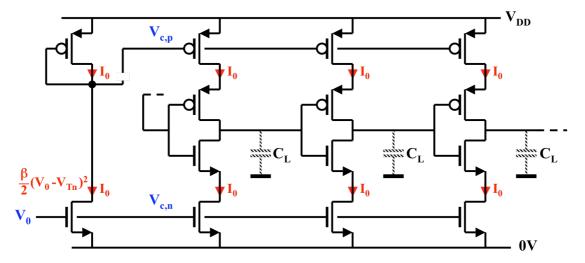

La limitation à une seule polarité pour  $V_2$  peut être éliminée par l'utilisation du circuit décrit ci-après, connu sous le nom de "multiplieur de Gilbert" ou "cellule de Gilbert", du nom de son inventeur, Mr. Barie Gilbert. Son schéma est le suivant:

Dans ce circuit, la simple source de courant commandée par  $V_2$  est remplacée par la paire différentielle du bas dont  $V_2$  est l'entrée. Ses deux collecteurs constituent donc deux sources de courant I et I', qui vont chacun polariser l'une des deux paires différentielles à transconductance variable du haut, l'une amplifiant  $+V_1$ , l'autre  $-V_1$ . Les collecteurs gauches, respectivement droites, des deux paires sont connectées en parallèle afin d'additionner leurs courants.

Si la paire différentielle du bas est fortement dégénérée :

$$I = \frac{I_0}{2} + \frac{V_2}{2 \cdot R_E}$$

et  $I' = \frac{I_0}{2} - \frac{V_2}{2 \cdot R_E}$

Pour la paire supérieure gauche :

$$I_{C1} = \frac{I}{2} + \frac{I}{2} \tanh\left(\frac{V_1}{2 \cdot U_T}\right) = \left(\frac{I_0}{4} + \frac{V_2}{4 \cdot R_E}\right) + \left(\frac{I_0}{4} + \frac{V_2}{4 \cdot R_E}\right) \tanh\left(\frac{V_1}{2 \cdot U_T}\right)$$

$$I_{C2} = \frac{I}{4} - \frac{I}{4} \tanh\left(\frac{V_1}{2 \cdot U_T}\right) - \left(\frac{I_0}{4} + \frac{V_2}{4 \cdot R_E}\right) - \left(\frac{I_0}{4} + \frac{V_2}{4 \cdot R_E}\right) \tanh\left(\frac{V_1}{2 \cdot U_T}\right)$$

$$I_{C2} = \frac{I}{2} - \frac{I}{2} \tanh(\frac{V_1}{2 \cdot U_T}) = \left(\frac{I_0}{4} + \frac{V_2}{4 \cdot R_E}\right) - \left(\frac{I_0}{4} + \frac{V_2}{4 \cdot R_E}\right) \tanh(\frac{V_1}{2 \cdot U_T})$$

Pour la paire supérieure droite, dont l'entrée est inversée :

$$I_{C3} = \frac{I'}{2} + \frac{I'}{2} \tanh\left(\frac{-V_1}{2 \cdot U_T}\right) = \left(\frac{I_0}{4} - \frac{V_2}{4 \cdot R_E}\right) + \left(\frac{I_0}{4} - \frac{V_2}{4 \cdot R_E}\right) \tanh\left(\frac{-V_1}{2 \cdot U_T}\right)$$

$$I_{C4} = \frac{I'}{2} - \frac{I'}{2} \tanh\left(\frac{-V_1}{2 \cdot U_T}\right) = \left(\frac{I_0}{4} - \frac{V_2}{4 \cdot R_E}\right) - \left(\frac{I_0}{4} - \frac{V_2}{4 \cdot R_E}\right) \tanh\left(\frac{-V_1}{2 \cdot U_T}\right)$$

Les courants des collecteurs connectés s'additionnant, et sachant que tanh(-x) = -tanh(x):

$$I_{A} = I_{C1} + I_{C3} = \frac{I_{0}}{2} + \frac{V_{2}}{2 \cdot R_{E}} \cdot \tanh \left( \frac{V_{1}}{2 \cdot U_{T}} \right)$$

$$I_B = I_{C2} + I_{C4} = \frac{I_0}{2} - \frac{V_2}{2 \cdot R_E} \cdot \tanh\left(\frac{V_1}{2 \cdot U_T}\right)$$

Et enfin:

$$V_{od} = R_C \cdot (I_A - I_B) = R_C \cdot \frac{V_2}{R_E} \cdot \tanh\left(\frac{V_1}{2 \cdot U_T}\right) = \frac{R_C}{R_E} \cdot V_2 \cdot \tanh\left(\frac{V_1}{2 \cdot U_T}\right)$$

Pour des signaux  $V_1$  limités à  $\pm 10$  mV autour de zéro, les approximations linéaires suivantes présentent une erreur maximum de 1%:

$$I_{A} = \frac{I_{0}}{2} + \frac{V_{2} \cdot V_{1}}{2 \cdot R_{F} \cdot 2 \cdot U_{T}}$$

et  $I_{B} = \frac{I_{0}}{2} - \frac{V_{2} \cdot V_{1}}{2 \cdot R_{F} \cdot 2 \cdot U_{T}}$

$$\mathbf{V_{od}} = \frac{\mathbf{R_C}}{\mathbf{R_E}} \cdot \mathbf{V_2} \cdot \frac{\mathbf{V_1}}{2 \cdot \mathbf{U_T}} = \frac{\mathbf{V_1} \cdot \mathbf{V_2}}{2 \cdot \mathbf{U_T} \cdot \mathbf{R_E} / \mathbf{R_C}}$$

On a bien le produit des signaux  $V_1$  et  $V_2$ , chacun pouvant être positif ou négatif, indépendamment l'un de l'autre, d'où l'appellation multiplicateur "quatre quadrants" (dans un plan  $V_1, V_2$ ).

La dynamique utile du signal  $V_2$  peut être fixée librement par le produit  $I_0R_E$ , par contre celle de  $V_1$  est limitée à environ  $\pm 10 \, \text{mV}$  autour de  $0 \, \text{V}$ .

Pour élargir la dynamique de l'entrée  $V_1$ , il n'est malheureusement pas possible de dégénérer les deux paires différentielles supérieures, car leur gain en tension ne serait alors plus proportionnel à  $g_m$ , ce qui supprimerait la fonction de multiplication recherchée.

#### 2.6.3 Applications du multiplieur analogique à cellule de "Gilbert"

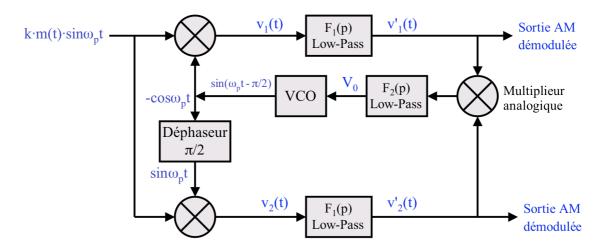

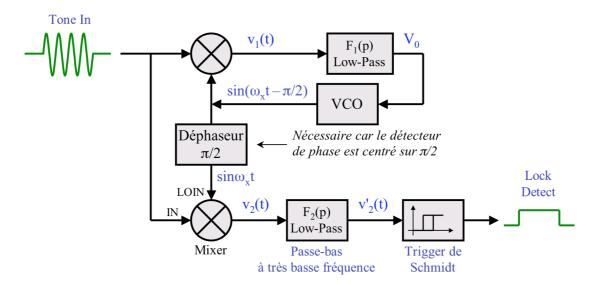

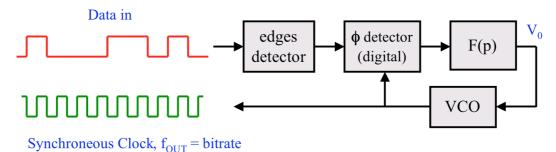

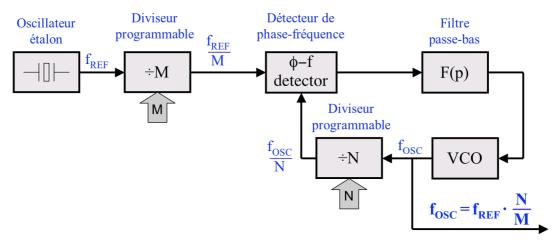

Les principales applications de la cellule de "Gilbert", appelée aussi modulateur équilibré (balanced modulator, balanced mixer), sont les suivantes:

- Modulation d'amplitude (AM):  $s_{AM}(t) = s_{source}(t) \cdot sin(2\pi \cdot f_{porteuse} \cdot t)$

- Démodulation AM synchrone:

$$\begin{array}{lll} s_{\text{AM}}(t) \cdot \sin(2\pi \cdot f_{\text{porteuse}} \cdot t) &= \left[ s_{\text{source}}(t) \cdot \sin(2\pi \cdot f_{\text{porteuse}} \cdot t) \right] \cdot \sin(2\pi \cdot f_{\text{porteuse}} \cdot t) \\ &= \frac{1}{2} \cdot s_{\text{source}}(t) - \frac{1}{2} \cdot s_{\text{source}}(t) \cdot \cos(2\pi \cdot 2f_{\text{porteuse}} \cdot t) \\ &= \frac{1}{2} \cdot s_{\text{source}}(t) & \text{après filtrage passe-bas} \end{array}$$

• Changement de fréquence:

$$\begin{array}{lll} \sin(2\pi\cdot f_1\cdot t)\cdot\sin(2\pi\cdot f_2\cdot t) &=& \frac{1}{2}\cdot\cos(2\pi\cdot (f_2-f_1)\cdot t) &-& \frac{1}{2}\cdot\cos(2\pi\cdot (f_2+f_1)\cdot t) \\ &=& \frac{1}{2}\cdot\cos(2\pi\cdot (f_2-f_1)\cdot t) & \text{après filtrage passe-bande} \\ &\text{ou } \frac{1}{2}\cdot\cos(2\pi\cdot (f_2+f_1)\cdot t) & \text{après filtrage passe-bande} \end{array}$$

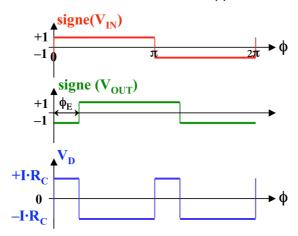

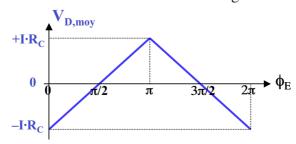

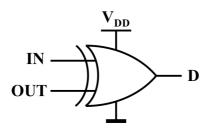

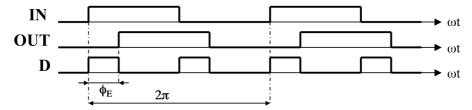

• Détection de phase:

$$\begin{array}{ll} \sin(2\pi\cdot f_1\cdot t+\phi)\cdot\sin(2\pi\cdot f_1\cdot t) &= \frac{1}{2}\cdot\cos(\phi) - \frac{1}{2}\cdot s_{\text{source}}(t)\cdot\cos(2\pi\cdot 2f_1\cdot t) \\ &= \frac{1}{2}\cdot\cos(\phi) & \text{après filtrage passe-bas} \end{array}$$

#### Circuits et Systèmes Electroniques Exercice Paire Différentielle

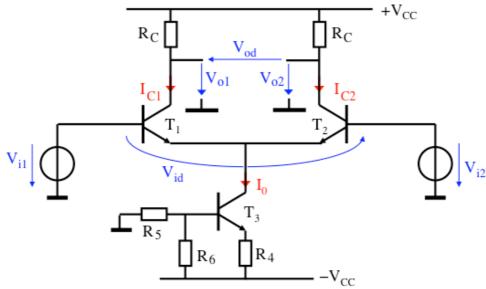

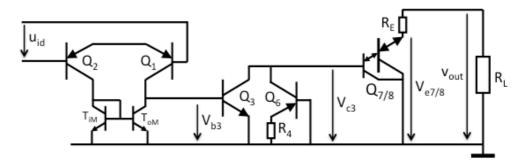

Soit la paire différentielle T<sub>1</sub>-T<sub>2</sub> avec sa source de courant de polarisation réalisée par T<sub>3</sub> :

Tous les transistors sont identiques :  $\beta = 300$ ,  $V_A = 75$  V  $R_C = 2$  k $\Omega$ ,  $R_4 = 1.5$  k $\Omega$ ,  $R_5 = 6.8$  k $\Omega$ ,  $R_6 = 3.9$  k $\Omega$ ,  $V_{CC} = 10$  V

#### Calculer:

- a) le courant de polarisation  $I_0$  ainsi que la résistance de sortie  $R_s$  de la source de courant ;

- b) la résistance d'entrée différentielle ;

- c) le gain en tension en mode différentiel des sorties asymétriques et différentielle (dite aussi symétrique);

- d) la résistance de sortie différentielle et celle des sorties asymétriques ;

- e) le gain en tension en mode commun des sorties asymétriques, ainsi que le taux de réjection de mode commun ;

- f) la dynamique des sorties ;

- g) la dynamique d'entrée en mode commun, garantissant encore un fonctionnement inchangé en mode différentiel avec la pleine dynamique de sortie.

## Circuits et Systèmes Electroniques Exercice Corrigé

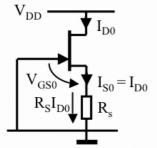

# a) Source de courant constant

Si l'on néglige le courant de base par rapport à celui à travers R<sub>5</sub> et R<sub>6</sub>

$$\frac{R_6}{U_{R6}} = V_{CC} \frac{R_6}{R_5 + R_6} \approx 3.64 \ V_{CC} \frac{V_{CC} \frac{R_5 + R_6}{R_5 + R_6} - U_j}{R_4} \approx 2 \ mA$$

La résistance de sortie est celle d'accès au collecteur de T3:

$$RS = \frac{1}{g_{ce3}} \cdot \frac{1 + g_{m3}RE + g_{be3}RB}{1 + g_{be3}(RE + RB)}$$

$$g_{m3} = \frac{I_0}{U_T} = 77 \text{ mA/V} \qquad g_{be3} = \frac{g_{m3}}{B_3} = 0.26 \text{ mA/V} \qquad g_{ce3} = \frac{I_0}{V_{A3}} = 27 \, \mu \text{A/V}$$

$$R_E = R_4 = 1500 \, \Omega >> \frac{1}{g_{m3}} = 13 \, \Omega \qquad R_B = R_5//R_6 = 2500 \, \Omega < \frac{1}{g_{be3}} = 3900 \, \Omega$$

$$R_{E}+R_{B}=R_{4}+(R_{5}/R_{6})=4000~\Omega\approx\frac{1}{gbe3}=3900~\Omega$$

$$\Rightarrow \quad R_S \approx \frac{1}{g_{ce3}} \cdot \frac{g_{m3}R_4}{1 + g_{be3}(R_4 + (R_5//R_6))} \approx 2 \; M\Omega$$

Au repos, chacun des transistors  $T_1$  et  $T_2$  est parcouru par  $\frac{I_0}{2}=1\ mA$  .

$$gm_{1ou2} = \frac{I_0/2}{U_T} = 38 \text{ mA/V}$$

$$gbe_{1ou2} = \frac{I_0/2}{B_{1ou2}U_T} = 0.13 \text{ mA/V}$$

$$gce_{1ou2} = \frac{I_0/2}{V_{A1ou2}} = 13 \mu\text{A/V}$$

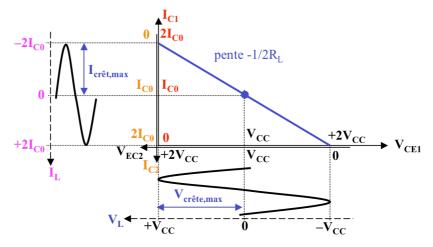

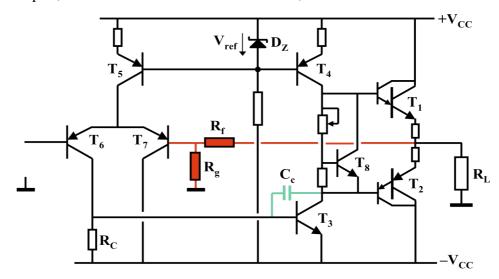

b), c) et d) Le demi-schéma équivalent en mode différentiel est :

ll s'agit donc d'un amplificateur Emetteur Commun

$$\frac{v_{o1}}{v_{i1}} = \frac{v_{o1}}{v_{id}/2} = -g_{m1}(R_C/\!/\!\frac{1}{g_{ce1}}) \ \approx -g_{m1}R_C \quad \text{ car } R_C = 2 \text{ kQ} << \frac{1}{g_{ce1}} = 77 \text{ kQ}$$

$$A_{vd1} = \frac{v_{o1}}{v_{id}} = -\frac{g_{m1}R_C}{2} = -\frac{I_0R_C}{4U_T} = -38 \qquad \text{(sortie asymétrique)}$$

$$A_{vd2} = \frac{v_{o2}}{v_{id}} = +\frac{g_{m2}R_C}{2} = +\frac{I_0R_C}{4U_T} = +38 \qquad \text{(sortie asymétrique)}$$

$$Avd = \frac{v_{id}}{v_{id}} = + g_{m1 ou2}R_{C} = + \frac{I_0R_{C}}{2U_{T}} = + 76 \quad \text{(sortie différentielle)}$$

$$R_{id} = \frac{v_{id}}{i_{id}} = \frac{2}{gbe} = 15 \text{ k}\Omega$$

$$R_{01} = R_{02} = (R_C / \frac{1}{g_{ce1ou2}}) \approx R_C = 2 \text{ kQ} \quad \text{ car } R_C = 2 \text{ kQ } << \frac{1}{g_{ce1ou2}} = 75 \text{ kQ}$$

$$R_{od}=R_{o1}+R_{o2}\approx 2R_C=4~k\Omega$$

e) Le demi-schéma équivalent en mode commun est :

Il s'agit donc d'un amplificateur Emetteur Commun Dégénéré

En négligeant gce (voir cours):

$$A_{vcm} = \frac{v_{oc}}{v_{icm}} = -\frac{g_{m1ou} 2R_C}{1 + g_{m1ou} 22R_S} \approx -\frac{R_C}{2R_S} = -5 \cdot 10^4$$

$$CMRR = \frac{|A_{vd1ou2}|}{|A_{vcm}|} = \frac{I_0R_C}{4U_T} \frac{2R_S}{R_C} = \frac{I_02R_S}{4U_T} = 7.6 \cdot 10^4$$

soit 98 dB

## f) La dynamique de sortie.

Avec une tension différentielle d'entrée  $v_{id} \approx \pm 100 \ mV$ , et si aucun transistor ne sature, tout le courant  $I_0$  (à moins de 2% près) passe dans l'un des transistors de la paire différentielle, et quasiment rien dans l'autre.

$$\begin{aligned} & Vol_{ou2,max} = VCC - R_{C} \cdot 0 = VCC = +10 \ V \\ & Vol_{ou2,min} = VCC - R_{C} \cdot I_0 = +6 \ V \\ & Vod_{,max} = + R_{C} \cdot I_0 = +4 \ V \\ & Vod_{,min} = -R_{C} \cdot I_0 = -4 \ V \end{aligned}$$

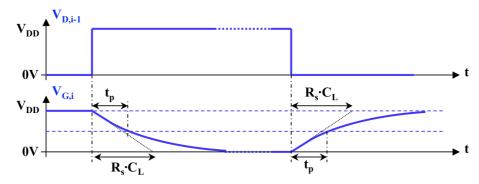

g) En présence de mode commun, la situation est la suivante :

La condition théorique pour qu'un transistor NPN ne sature pas est:

$$V_{CB} \ge 0$$

<=>  $V_C \ge V_B$  <=>  $V_{CE} \ge U_j \approx 0.7 \text{ V}$

Dans la pratique on peut tolérer :

$$V_{CB} \ge -0.4 \text{ V}$$

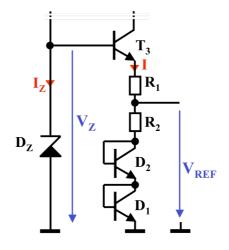

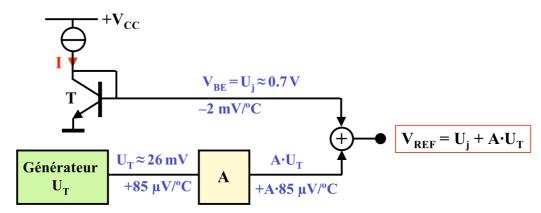

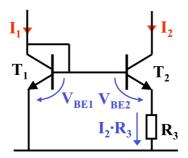

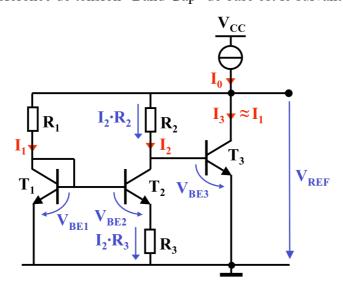

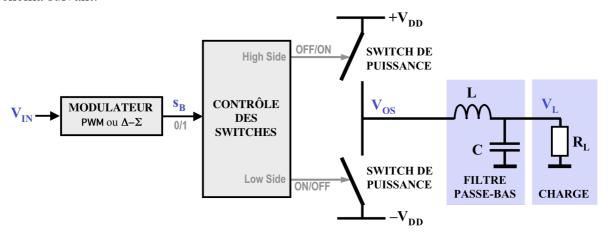

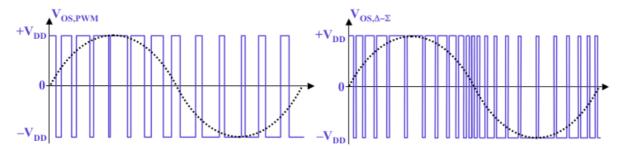

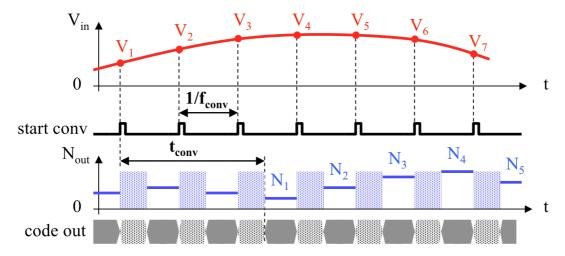

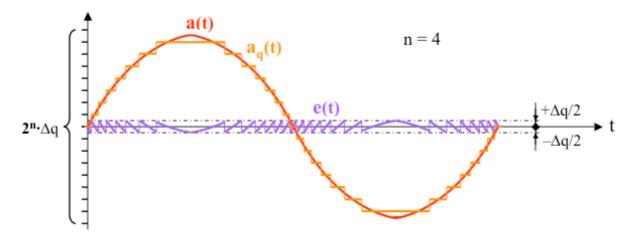

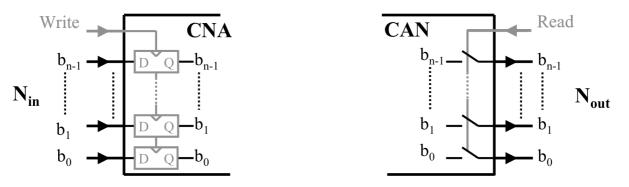

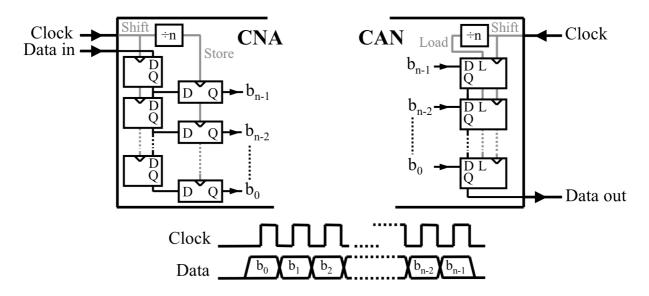

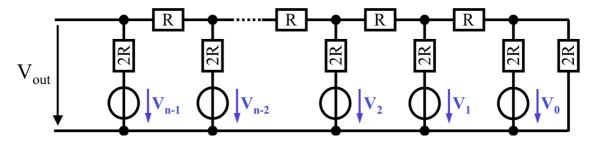

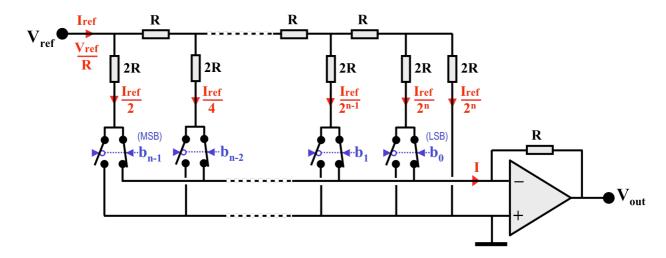

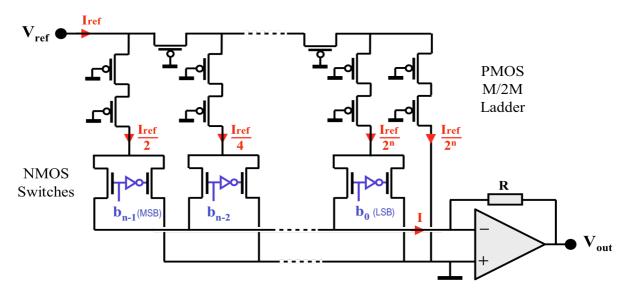

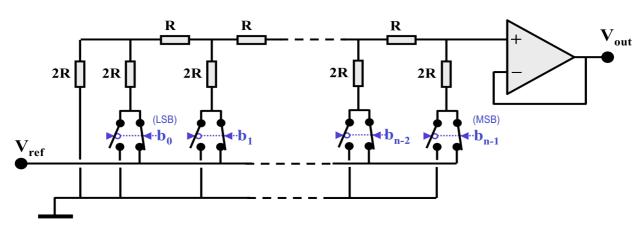

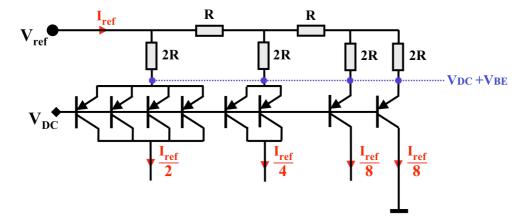

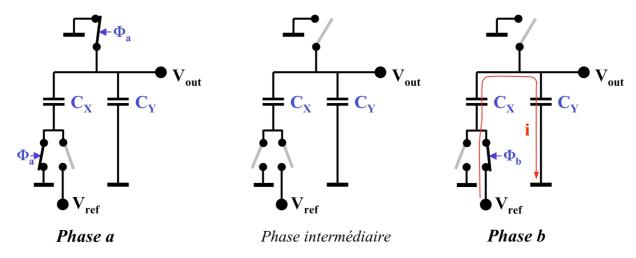

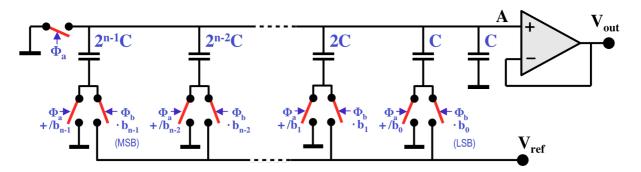

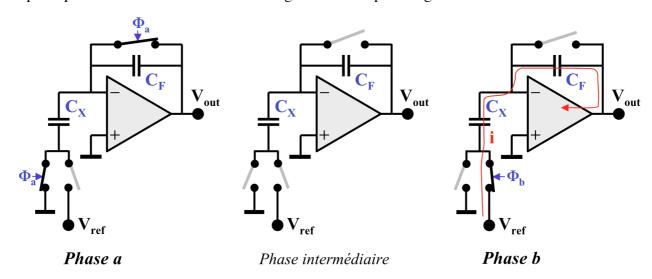

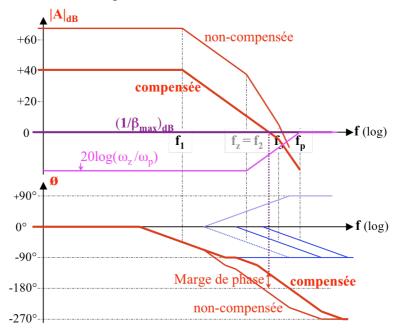

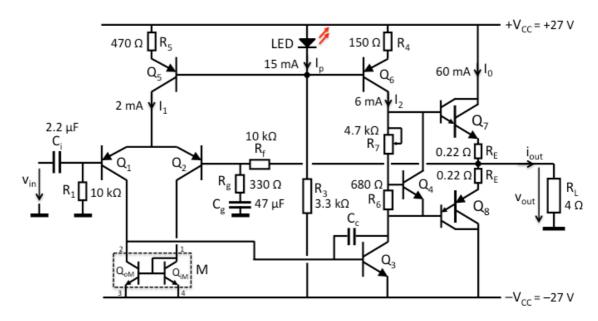

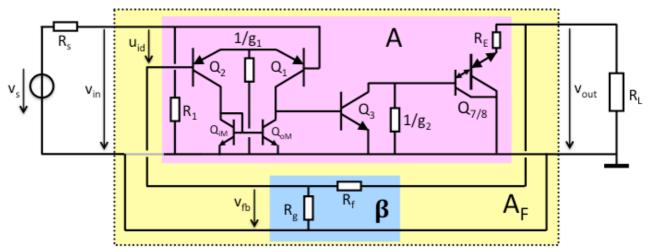

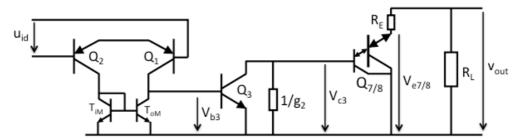

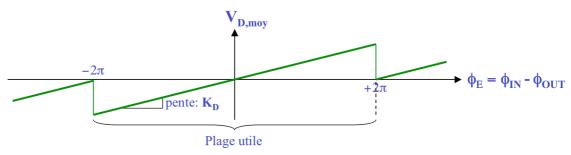

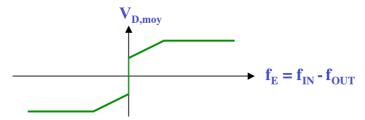

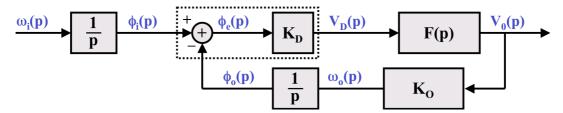

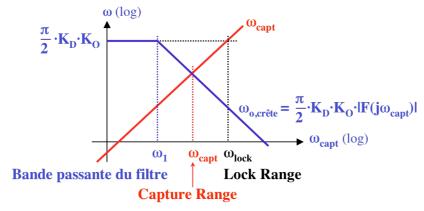

<=>  $V_{CE} \ge 0.3 \text{ V}$